# Universidad de Alcalá Escuela Politécnica Superior

# GRADO EN INGENIERÍA ELECTRÓNICA DE COMUNICACIONES

Trabajo Fin de Grado

Desarrollo de un backend para un receptor radioastronómico de ocultaciones lunares

# ESCUELA POLITECNICA SUPERIOR

Autor: Alberto Río Martínez

Ingeniero que avala el proyecto: Pablo García Carreño

Tutor colaborador de la UAH: Raúl Mateos Gil

#### Resumen

El presente Trabajo Fin de Grado tiene como objetivo fundamental el diseño de un sistema basado en un SoC (System on Chip) programable que permita realizar, en tiempo real, la Transformada Rápida de Fourier sobre señales obtenidas mediante observaciones lunares.

Este trabajo constituye la primera aproximación al uso de FPGAs para la implementación de back-ends radioastronómicos del Observatorio de Yebes, institución que financia y avala el proyecto. Para llevar a cabo esta tarea, se ha optado por emplear la tarjeta de evaluación Zedboard y el conversor analógico digital AD9467, los cuales se pueden conectar entre ellos.

**Palabras clave:** Zedboard, Backend de recepción radioastronómica, Acceso Directo a Memoria, AD9467, Procesamiento digital de señales con algoritmo FFT.

#### **Abstract**

The main goal of the following project is the design of a system based on a programmable SoC (System on Chip) that allows performing, in real time, the Fast Fourier Transform on signals from lunar observations.

This project means the first approach of the "Observatorio de Yebes" on the use of FPGAs for implement radio astronomy back-ends. To carry out this task, the chosen devices are Zedboard evaluation card and AD9467 analog-to-digital converter, which can stablish connections among them.

**Main words:** Zedboard, Radio Astronomy Reception Back-End, Direct Memory Access, AD9467, Digital signal processing with FFT algorithm.

#### Resumen extendido

El uso de FPGAs en observaciones astronómicas está muy extendido en la actualidad debido a la gran escalabilidad y calidad que pueden llegar a ofrecer. Sin duda, una de las principales razones de este auge, es el considerable aumento en la fiabilidad de los sistemas basados en estos dispositivos, ya que, las funciones que desempeñan implican un menor número de integrados en la placa de circuitos y, por ende, una reducción en el número de fallos de los mismos [1].

Sin embargo, la razón principal para el uso de estos dispositivos en radioastronomía es la creciente necesidad de procesar grandes cantidades de datos a la máxima velocidad posible. En este marco los SoC basados en FPGA son ideales, ya que ofrecen la escalabilidad y reprogramabilidad de las FPGA ligado a las velocidades de procesamiento del SoC.

El Observatorio de Yebes es una unidad del Instituto Geográfico Nacional dedicada al desarrollo y construcción de instrumentación en el campo de la radioastronomía [2]. Nanocosmos es uno de los numerosos proyectos en los que esta organización se ve envuelta. Su objetivo principal es revelar las condiciones físicas y químicas en la zona de formación de polvo cósmico de las estrellas evolucionadas, haciendo uso de las nuevas técnicas y capacidades de observación. Una de esas técnicas es la observación de ocultaciones lunares, para las cuales son necesarios back-ends de recepción de una resolución mayor a la de los que dispone el Observatorio actualmente.

Las ocultaciones lunares consisten en la alineación o interposición de un cuerpo celeste por la luna. Para realizar la observación de dicho fenómeno, hay que realizar un barrido de datos a muy alta frecuencia y en tiempo real. Uno de los principales problemas que presenta dicha observación es el procesado y tratamiento de grandes volúmenes de datos a muy alta velocidad, por lo que es conveniente el uso de implementaciones basadas en FPGAs, no solo por la velocidad que ofrecen, sino por los múltiples modos de operación que permiten desarrollar.

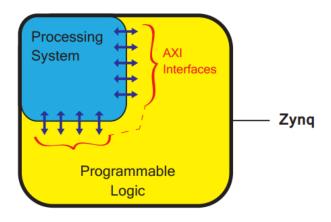

Para este diseño se pretende utilizar la tarjeta Zedboard, una SoC basado en FPGA de la familia Zynq de Xilinx. Este tipo de dispositivo consta de dos bloques principales. El primero de ellos, denominado Processing System o PS, está compuesto por un procesador ARM9 de doble núcleo y toda una serie de periféricos y controladores de memoria necesarios para su operación. El otro bloque, denominado Programmable Logic o PL, es un bloque donde se modela la lógica configurable. Ambos bloques se conectan mediante enlaces AXI (Advanced eXtensible Interface). Mientras que la lógica programable provee de funcionalidades como lógica de alta velocidad o aritmética, el sistema de procesamiento proporciona soporte para la ejecución de rutinas software y/o sistemas operativos.

El sistema constará de una primera etapa de adquisición y digitalización de los datos, tarea que se llevará a cabo con el conversor analógico digital AD9467, el cual está

conectado a la tarjeta Zedboard por medio de un puerto de alta velocidad de la misma. En la etapa intermedia los datos serán procesados por un bloque que aplicará el algoritmo de la Transformada rápida de Fourier sobre ellos. Por último, se procederá a almacenar los datos en memoria haciendo uso de un controlador de DMA (Direct Memory Access). En el diseño de este enlace de comunicación se buscará la reducción del consumo de recursos.

El Observatorio de Yebes está muy interesado en este tipo de proyectos, hasta el punto de que tiene como objetivo crear un grupo de trabajo dedicado a la generación de back ends con SoCs basados en FPGA. Este proyecto implica una de las primeras aproximaciones de la organización a este tipo de sistemas, y debido a la gran escalabilidad de los mismos podría servir de base a nuevos proyectos de back-ends dedicados a otro tipo de observaciones.

### Índice

| RESUMEN                                                                                             | 3  |

|-----------------------------------------------------------------------------------------------------|----|

| ABSTRACT                                                                                            | 4  |

| RESUMEN EXTENDIDO                                                                                   | 5  |

| ÍNDICE                                                                                              | 7  |

| ÍNDICE DE FIGURAS                                                                                   | 9  |

| CAPÍTULO 1: INTRODUCCIÓN                                                                            | 13 |

| 1.1 OBJETIVOS DEL PROYECTO                                                                          | 13 |

| 1.2 Organización de la memoria                                                                      | 13 |

| CAPÍTULO 2: INTRODUCCIÓN TEÓRICA                                                                    | 16 |

| 2.1 Radioastronomía                                                                                 | 16 |

| 2.1.1 Contexto histórico                                                                            | 16 |

| 2.1.2 Gestión del espectro en radioastronomía                                                       | 20 |

| 2.2 EL RADIOTELESCOPIO                                                                              | 23 |

| 2.3 EL RECEPTOR RADIOASTRONÓMICO                                                                    | 25 |

| 2.4 VLBI                                                                                            | 26 |

| 2.5 Ocultaciones lunares                                                                            | 28 |

| 2.6 FPGAs                                                                                           | 30 |

| 2.7 Uso de FPGAs en radioastronomía                                                                 | 33 |

| 2.8 Observatorio de Yebes                                                                           | 34 |

| CAPÍTULO 3: DESCRIPCIÓN DEL HARDWARE E INTRODUCCIÓN AL DESARROLLO DE UN SISTEMA                     |    |

| BASADO EN ZYNQ                                                                                      | 36 |

| 3.1 Tarjeta de desarrollo Zedboard                                                                  | 37 |

| 3.1.1 Sistema de procesamiento (PS)                                                                 |    |

| 3.1.2 Lógica Programable (PL)                                                                       |    |

| 3.2 PERIFÉRICOS EN ZYNQ                                                                             |    |

| 3.3 CONEXIONES EN ZEDBOARD                                                                          |    |

| 3.4 Protocolo AXI                                                                                   |    |

| 3.4.1 AXI4-Stream                                                                                   |    |

| 3.5 AD9467-FMC-250EBZ                                                                               |    |

| 3.5.1 AD9467                                                                                        |    |

| 3.5.2 AD9517                                                                                        |    |

| 3.6 DESARROLLO DEL DISEÑO HARDWARE CON XILINX VIVADO                                                |    |

| 3.7 DESARROLLO DEL DISEÑO SOFTWARE CON XILINX SDK                                                   |    |

| CAPÍTULO 4: DESARROLLO DEL BACKEND                                                                  |    |

|                                                                                                     |    |

| 4.1 Creación de la interfaz axi_adc_controller para el ADC                                          |    |

| 4.1.1 Interfaz SPI                                                                                  |    |

| 4.1.2 Interfaz física                                                                               |    |

| 4.1.3 Banco de registros                                                                            |    |

| 4.1.4 Librerías para el software                                                                    |    |

| 4.2 CREACIÓN DE LA INTERFAZ "SYS_FFT" PARA LA GENERACIÓN DE LA TRANSFORMADA DE FOURIER DE LOS DATOS |    |

| 4.2.1 Banco de registros:                                                                           |    |

| 4.2.2 Librerías para el software.  4.3 BLOQUE DMA (DIRECT MEMORY ACCESS)                            |    |

|                                                                                                     | OC |

| 4.4 DESARROLLO HARDWARE                        | 92  |

|------------------------------------------------|-----|

| 4.5 DESARROLLO SOFTWARE                        | 106 |

| 4.6 CONSUMO DE RECURSOS EN EL SISTEMA          | 108 |

| 4.7 RESULTADOS                                 | 113 |

| CONCLUSIONES Y LÍNEAS FUTURAS DE INVESTIGACIÓN | 115 |

| Conclusiones                                   | 115 |

| LÍNEAS FUTURAS DE INVESTIGACIÓN                |     |

| BIBLIOGRAFÍA                                   | 117 |

## Índice de figuras

| ura 1: Ventanas atmosféricas para la radiación electromagnética (extraída de                           |          |

|--------------------------------------------------------------------------------------------------------|----------|

| HTTPS://WWW.QSL.NET/EA1CRK/MEDIO/CAP4.HTM)                                                             | 16       |

| Figura 2: A la izquierda, antena de Karl Jansky (extraído de https://alpoma.net/tecob/?p=5240), a la   | DERECHA, |

| ANTENA DE GROTE REBER (EXTRAÍDO DE HTTPS://WWW.ASTROMIA.COM/FOTOHISTORIA/TELESCOPIOREBER.F             | тм)17    |

| FIGURA 3: RADIOTELESCOPIO DE 14 M DEL OBSERVATORIO ASTRONÓMICO DE YEBES [15].                          | 18       |

| FIGURA 4: RADIOTELESCOPIO DE 40 METROS DEL OBSERVATORIO DE YEBES [15].                                 | 19       |

| Figura 5: Partes del radiotelescopio (extraída de                                                      |          |

| HTTP://GIOMEPE1214.BLOGSPOT.COM/2017/09/RADIOTELESCOPIO.HTML)                                          | 23       |

| FIGURA 6: DIAGRAMA DE BLOQUES DE UN RADIOTELESCOPIO                                                    | 24       |

| FIGURA 7: POSICIÓN DE LOS RADIOTELESCOPIOS DE LA RED EUROPEA DE VLBI [15].                             | 27       |

| Figura 8: Tipos de ocultaciones según la alineación de los cuerpos entre los que tiene lugar el fenóme | NO [5].  |

|                                                                                                        | 28       |

| FIGURA 9: DIAGRAMA DE BLOQUES DE LOS PRIMEROS CLB [14].                                                | 30       |

| FIGURA 10: ARQUITECTURA DE UN CLB (EXTRAÍDA DEHTTPS://WWW.ALDEC.COM/EN/COMPANY/BLOG/144                |          |

| INTRODUCTION-TO-ZYNQ-ARCHITECTURE).                                                                    | 31       |

| Figura 11: Modelo simplificado de la arquitectura Zynq [7]                                             | 36       |

| Figura 12: Diagrama de bloques de la APU.                                                              | 37       |

| Figura 13: Partes de la Zedboard.                                                                      |          |

| Figura 14: Ejemplo de comunicación AXI-Stream [8]                                                      |          |

| Figura 15: Arquitectura del AD9467 [16].                                                               |          |

| Figura 16: Diagrama temporal de las señales del AD9467 [16].                                           |          |

| Figura 17: Comunicación SPI [16].                                                                      | 49       |

| FIGURA 18: DIAGRAMA DE BLOQUES DEL AD9517 [17].                                                        |          |

| FIGURA 19: CONEXIONADO DEL AD9517 EN LA TARJETA AD9467-FMC-250EBZ [18].                                |          |

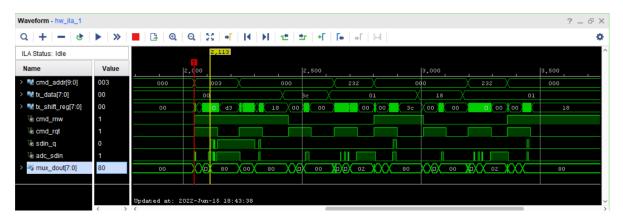

| FIGURA 20: RESULTADO DEL TEST DE LA COMUNICACIÓN SPI CON EL COMPONENTE AD9467.                         | 63       |

| FIGURA 21: RESULTADO DEL TEST DE LA COMUNICACIÓN SPI CON EL COMPONENTE AD517.                          |          |

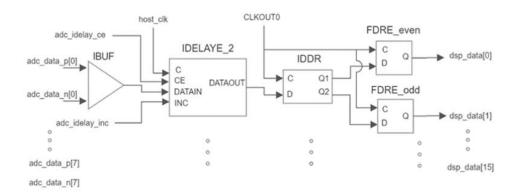

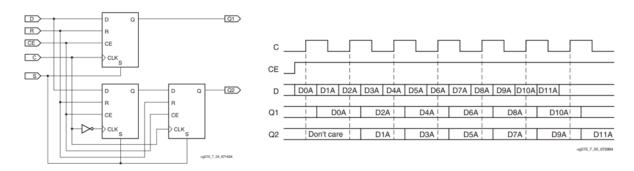

| FIGURA 22: ARQUITECTURA HARDWARE CORRESPONDIENTE AL BLOQUE DE RETARDO.                                 |          |

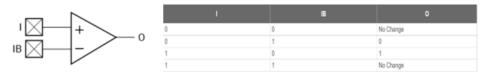

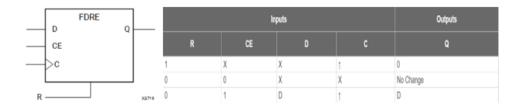

| FIGURA 23: REPRESENTACIÓN DEL COMPONENTE Y TABLA DE VERDAD [9]                                         |          |

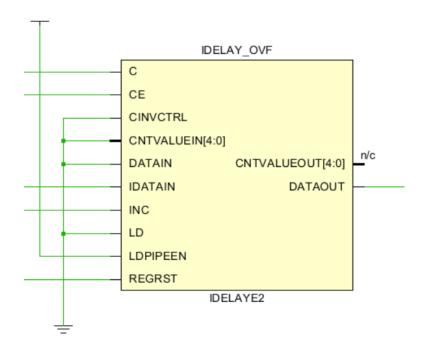

| FIGURA 24: CONEXIONADO DEL COMPONENTE IDELAYE2.                                                        |          |

| Figura 25: A la izquierda, registros de entrada DDR y señales asociadas en el modo same Edge. A la de  |          |

| DIAGRAMA TEMPORAL QUE ILUSTRA EL FUNCIONAMIENTO DE DICHAS SEÑALES. [20].                               |          |

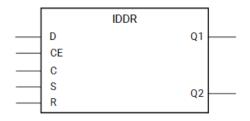

| FIGURA 26: BLOQUE REPRESENTATIVO DEL COMPONENTE IDDR [9].                                              |          |

| FIGURA 27: REPRESENTACIÓN DEL COMPONENTE Y TABLA DE VERDAD [9]                                         |          |

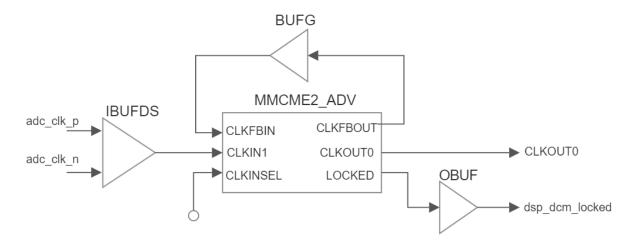

| FIGURA 28: DIAGRAMA ILUSTRATIVO DEL BLOQUE DE PROCESAMIENTO DE LA SEÑAL DE RELOJ                       |          |

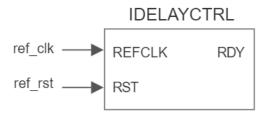

| FIGURA 29: DIAGRAMA ILUSTRATIVO DEL BLOQUE DE CONTROL DEL COMPONENTE IDELAY.                           | 71       |

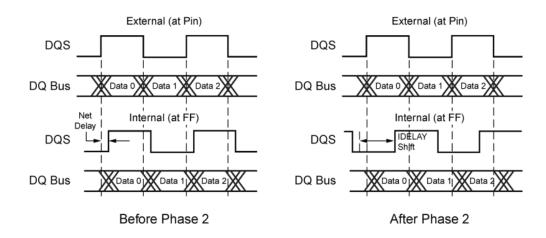

| Figura 30: Proceso de calibración del bus de datos (extraído de                                        |          |

| https://support.xilinx.com/s/article/43667?language=en_US)                                             |          |

| FIGURA 31: PATRONES DE TESTEO DEL AD9467 [16]                                                          |          |

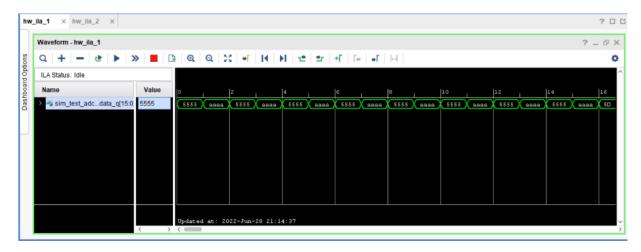

| FIGURA 32: LÍNEA DE DATOS DEL ADC EN MODO CHECKERBOARD CALIBRADOS.                                     |          |

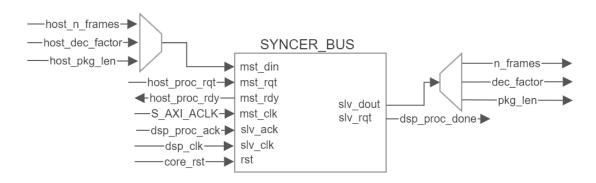

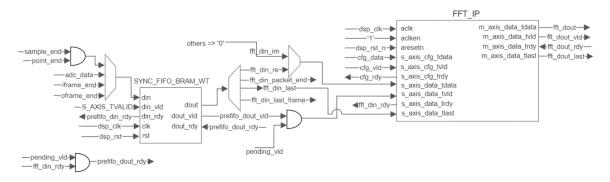

| FIGURA 33: DIAGRAMA DE BLOQUES DE LA ETAPA DE SINCRONIZACIÓN DE LAS SEÑALES DE INFORMACIÓN DE TRANSM   |          |

| FIGURA 34: DIAGRAMA DE BLOQUES DE LA ETAPA DE PREFIFO Y BLOQUE FFT.                                    |          |

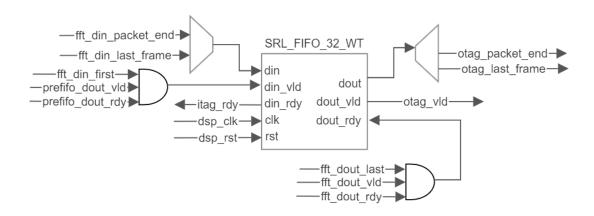

| FIGURA 35: DIAGRAMA DE BLOQUES DE LA ETAPA DE FIFO PARA LA OBTENCIÓN DE LAS SEÑALES DE ÚLTIMA TRAMA Y  |          |

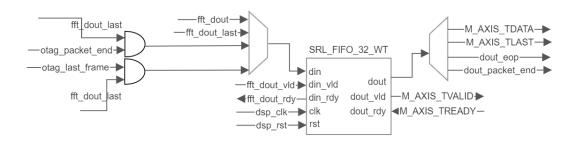

| PAQUETE                                                                                                |          |

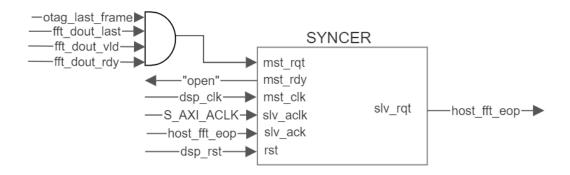

| FIGURA 36: DIAGRAMA DE BLOQUES DE LA ETAPA DE POSTFIFO                                                 |          |

| FIGURA 37: DIAGRAMA DE BLOQUES DE LA ETAPA DE SINCRONIZACIÓN PARA LA OBTENCIÓN DE INTERRUPCIÓN         |          |

| FIGURA 38: DIAGRAMA REPRESENTATIVO DE LA MÁQUINA DE ESTADOS DE UN BD [11]                              |          |

| FIGURA 39: BLOQUE ZYNQ7 PROCESSING SYSTEM.                                                             |          |

| FIGURA 40: ASISTENTE GRÁFICO PARA CONFIGURACIÓN DEL BLOQUE IP                                          |          |

| FIGURA 41: BLOOUF IP AXI INTERCONNECT                                                                  | 95       |

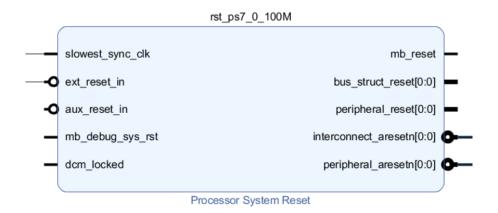

| Figura 42: Bloque IP Processor System Reset                                                              | 96  |

|----------------------------------------------------------------------------------------------------------|-----|

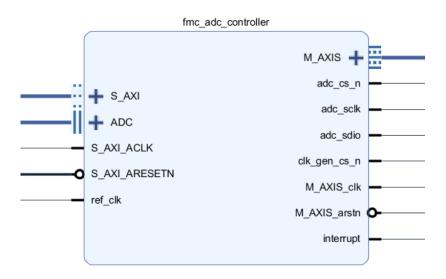

| FIGURA 43: BLOQUE IP AXI ADC CONTROLLER.                                                                 | 97  |

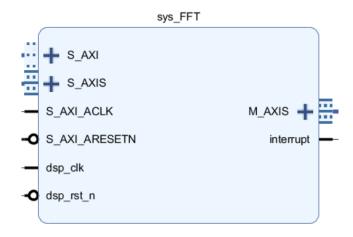

| FIGURA 44: BLOQUE IP SYS_FFT.                                                                            | 99  |

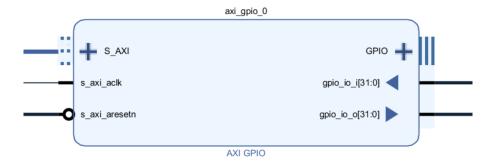

| FIGURA 45: BLOQUE IP AXI GPIO.                                                                           | 100 |

| FIGURA 46: BLOQUE IP AXI DIRECT MEMORY ACCESS                                                            | 101 |

| Figura 47: Diagrama de bloques del sistema.                                                              | 102 |

| FIGURA 48: ASISTENTE PARA ASIGNACIÓN DE BANCOS DE MEMORIA DE VIVADO                                      | 103 |

| Figura 49: Representación del modelo implementado del sistema.                                           | 104 |

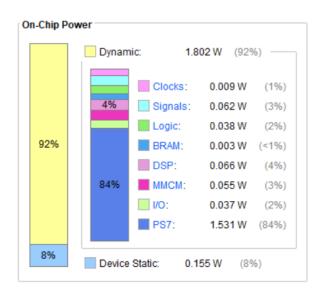

| Figura 50: Gráfico de la optimización de consumo del sistema                                             | 105 |

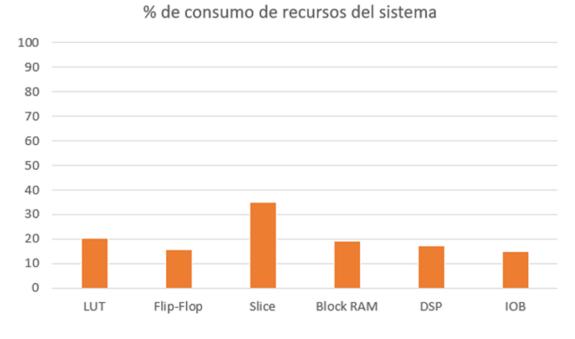

| Figura 51: Gráfica del porcentaje de consumo de recursos del sistema                                     | 108 |

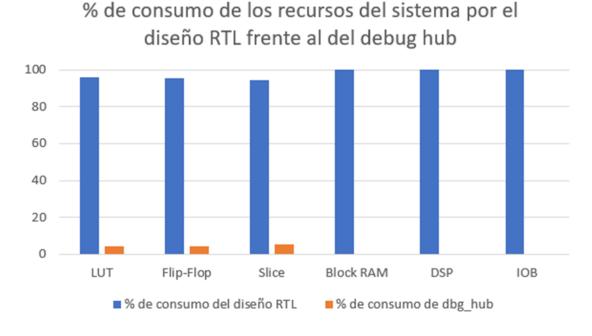

| FIGURA 52: GRÁFICA DE PROCENTAJE DE CONSUMO DE RECURSOS DEL SISTEMA POR EL DISEÑO RTL FRENTE AL DEL DEBI |     |

| HUB                                                                                                      | 109 |

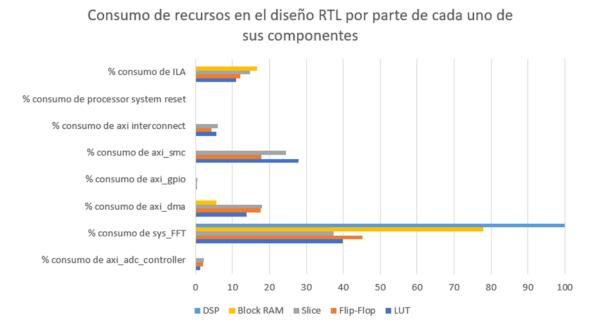

| FIGURA 53: GRÁFICA DE CONSUMO DE RECURSOS EN EL DISEÑO RTL POR PARTE DE CADA UNO DE SUS COMPONENTES      | 112 |

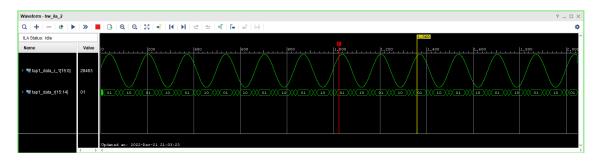

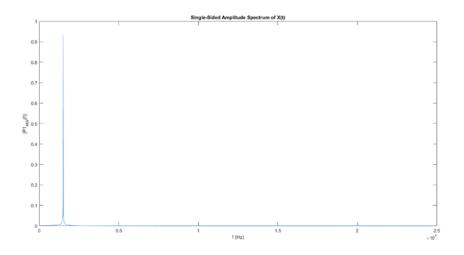

| FIGURA 54: SEÑAL APLICADA PARA EL TEST DE FRECUENCIA CONSTANTE                                           | 113 |

| FIGURA 55: REPRESENTACIÓN DE LA FFT DE LOS DATOS REALIZADA EN MATLAB                                     | 113 |

### Índice de tablas

| Tabla 1: Tabla de datos de consumo del sistema frente a la totalidad de recursos disponibles en Ze | DBOARD |

|----------------------------------------------------------------------------------------------------|--------|

|                                                                                                    | 108    |

| Tabla 2: Tabla de consumo de recursos del sistema por el diseño RTL frente al del debug hub        |        |

| TABLA 3: TABLA DE CONSUMO DE RECURSOS DEL SISTEMA POR AXI_ADC_CONTROLLER                           | 110    |

| Tabla 4: Tabla de consumo de recursos del sistema por sys_FFT                                      | 110    |

| Tabla 5: Tabla de consumo de recursos del sistema por axi_dma                                      | 110    |

| Tabla 6: Tabla de consumo de recursos del sistema por axi_gpio                                     | 110    |

| TABLA 7: TABLA DE CONSUMO DE RECURSOS DEL SISTEMA POR AXI_SMC                                      | 11     |

| Tabla 8: Tabla de consumo de recursos del sistema por axi interconnect                             | 11     |

| TABLA 9: TABLA DE CONSUMO DE RECURSOS DEL SISTEMA POR PROCESSOR SYSTEM RESET                       | 11     |

| TABLA 10: TABLA DE CONSUMO DE RECURSOS DEL SISTEMA POR EL ILA.                                     | 11     |

#### Capítulo 1: Introducción

#### 1.1 Objetivos del proyecto

Las dos principales virtudes que presentan los SoC basados en FPGA son las altas velocidades de procesamiento que pueden llegar a ofrecer y la flexibilidad que brinda su implementación, lo que facilita en gran medida la realización de operaciones lógicas a muy alta velocidad. Esta funcionalidad es ideal a la hora de desarrollar algoritmos matemáticos como los implicados en el cálculo de la Transformada de Fourier.

El objetivo fundamental del proyecto es el diseño e implementación en Zedboard de un sistema de adquisición capaz de procesar señales, provenientes de observaciones radioastronómicas, adquiridas con velocidades de muestreo de 50 MHz.

Este trabajo queda englobado dentro del proyecto Nanocosmos en el cual se encuentra incluido el Observatorio Astronómico de Yebes, donde se pretende diseñar y realizar este back-end.

#### 1.2 Organización de la memoria

Para abordar con éxito los objetivos impuestos se va a estructurar el diseño en tres bloques:

- 1. Bloque de adquisición y calibración de datos con el conversor analógico digital AD9467.

- 2. Bloque de procesamiento de los datos adquiridos aplicando el algoritmo de la Transformada Rápida de Fourier.

- 3. Bloque de acceso directo a memoria haciendo uso del controlador DMA de la tarjeta de desarrollo.

Una vez funcionen estos tres bloques de manera independiente, se unirán para crear el sistema final. Para abordar estos bloques de manera efectiva es precisa una base teórica tanto de radioastronomía como de diseño de sistemas de adquisición con SoC basados en FPGA.

A continuación, se expondrán los capítulos conformantes de esta memoria con el fin de esclarecer el contenido de los mismos:

El primer capítulo supone una introducción al documento, y trata de exponer los objetivos del proyecto y el procedimiento empleado para alcanzarlos.

El segundo capítulo supone una introducción teórica a algunos conceptos básicos de radioastronomía y FPGAs que ayudarán a contextualizar el proyecto.

En el tercer capítulo se trata de dar una explicación del hardware empleado, así como de las conectividades que presenta y las herramientas empleadas para desarrollar el proyecto.

El capítulo cuarto hace referencia al desarrollo del proyecto tanto a nivel hardware como a nivel software, así como a las pruebas y resultados obtenidos.

Por último, el documento consta de un apartado donde se exponen las conclusiones tras el desarrollo del proyecto y posibles campos de estudio futuros.

#### Capítulo 2: Introducción teórica

#### 2.1 Radioastronomía

La radioastronomía es una rama de la astronomía encargada de estudiar los cuerpos celestes por medio de sus emisiones en el dominio radioeléctrico. El nivel de potencia de estas señales es extremadamente débil. Eso hace que su recepción sea muy compleja requiriendo dispositivos diseñados ad hoc para esta tarea, como los radiotelescopios. Generalmente, los radiotelescopios consisten en una gran antena parabólica capaz de captar ondas electromagnéticas.

#### 2.1.1 Contexto histórico

Casi todo lo que sabemos sobre el espacio, es decir, las estrellas y el medio interestelar, se ha obtenido de la radiación electromagnética. Los portadores de información material (meteoritos que impactan la tierra, partículas de rayos cósmicos o muestras de material recolectado) nos proveen una información ínfima a su lado [3].

La radiación electromagnética que proviene del espacio es absorbida, en su gran mayoría, por la atmósfera terrestre. Sin embargo, existen bandas para las cuales la atmósfera es transparente, y son dos de estas bandas las que destacan notablemente sobre las demás por su anchura. La primera de estas bandas es la ventana óptica, que comprende las ondas electromagnéticas pertenecientes al espectro visible, con longitudes de onda desde los 300 a los 1000 nm. La segunda es la ventana radio, que es la que nos ocupa, y comprende longitudes de onda de entre 1 mm y 15 m (300 GHz a 20 MHz). La Figura 1 muestra un diagrama con las ventanas para la radiación electromagnética.

#### VENTANAS ATMOSFÉRICAS PARA LA RADIACIÓN ELECTROMAGNÉTICA Longitud de onda en nanómetros $1 \text{ km} = 10^{12} \text{ nm}$ 10 m mm cm = 1010 106 108 B E B m Ondas de radio Rayos X Infrarrojo Absorción por gas interestelar Opacidad Ventana de radio debida a la Ventana Ionosfera

Figura 1: Ventanas atmosféricas para la radiación electromagnética (extraída de https://www.qsl.net/ea1crk/medio/Cap4.htm).

Durante muchos años, la humanidad estuvo restringida a las mediciones realizadas en lo visible. No fue hasta la época de Herschel cuando este rango de longitud de onda se amplió ligeramente hasta longitudes de onda cercanas al infrarrojo, y en 1930, se extendió desde el ultravioleta cercano hasta el infrarrojo cercano:  $0.35 \mu m \le \lambda \le 1 \mu m$ .

En 1932, Karl Jansky realizó las primeras observaciones radioastronómicas en los laboratorios de Bell Telephone. Allí consiguió captar una señal a 20,5MHz investigando interferencias radioeléctricas. Tras esto, continuó sus observaciones sin mucho impacto hasta que, en 1937, Grote Reber llevó a cabo mediciones de ondas a 160 MHz con un instrumento que desarrolló a partir de las investigaciones de Jansky, y que hoy en día se considera como el primer prototipo de radiotelescopio. Operando en esas frecuencias consiguió captar ondas provenientes del plano de la vía láctea, con las que pudo desarrollar los primeros mapas del cielo en frecuencias de radio, los cuales publicó en 1944. La Segunda Guerra Mundial derivó en una mejora considerable en los receptores para uso militar, pero, una vez concluyó, algunos investigadores dirigieron su atención hacia el "ruido" de radio proveniente de fuentes extraterrestres [3]. La Figura 2 muestra las antenas desarrolladas por Jansky y Reber.

Figura 2: A la izquierda, antena de Karl Jansky (extraído de https://alpoma.net/tecob/?p=5240), a la derecha, antena de Grote Reber (extraído de https://www.astromia.com/fotohistoria/telescopioreber.htm).

Más tarde, las observaciones se vieron ampliadas hasta el infrarrojo intermedio por Pettit y Nicholson, alcanzando longitudes de onda de 1 a 4 micras. Fueron seguidas por las primeras observaciones de estrellas en el infrarrojo lejano, de longitudes de onda de 8 a 14 micras y 4 a 5.5 micras, y fueron desarrolladas por Murray, Wildey, Johnson y Mitchell. Por último, en 1965 Arno Penzias y Robert Wilson captaron accidentalmente la radiación cósmica de fondo trabajando con una antena de bocina de 6 metros, hallazgo por el cual recibieron el premio Nobel en el año 1978.

Este ha sido un pequeño repaso histórico de los inicios de la radioastronomía a nivel global, pero también es interesante exponer algunos de los hallazgos de la radioastronomía en España. El Observatorio de Yebes ha sido una parte fundamental de dichos hallazgos y es una instalación muy importante a nivel internacional.

En la década de 1970, gracias a los Planes de Desarrollo, el Real Observatorio de Madrid (ROM) recibió una inyección de capital que empleó en crear el Observatorio de Yebes. La instrumentación desarrollada para este centro consistía en un astrógrafo doble de 40 cm, un telescopio óptico infrarrojo de 1,5 m de diámetro y un radiotelescopio de 14 m de diámetro para longitudes de onda milimétricas, mostrado en la Figura 3. Este último fue de vital importancia, ya que con él se comenzaron las observaciones de Interferometría de Muy Larga Base (VLBI) en el Observatorio y se llevó a cabo una de las principales aportaciones científicas del momento en el panorama nacional. Esta consistía en el seguimiento de las variaciones de intensidad de la emisión de los máseres circunestelares de óxido de silicio en estrellas evolucionadas.

Figura 3: Radiotelescopio de 14 m del Observatorio Astronómico de Yebes [15].

La creciente mejora de los instrumentos radioastronómicos a finales de los años 80 y principios de los 90 ocasionó una demanda de mejora en las instalaciones del Observatorio de Yebes. En este contexto, para mantener y desarrollar la radioastronomía experimental en España era preciso dejar a un lado el radiotelescopio de 14 metros y desarrollar uno nuevo de mayores prestaciones. Se determinó que la instalación idónea a generar era un radiotelescopio de 40 metros, el cual fue inaugurado el 26 de abril de 2005 y se muestra en la Figura 4. No fue hasta 2007 cuando se llevó a cabo la primera prueba de observación, y en 2008 se realizó la primera observación VLBI. A partir de este punto, el radiotelescopio de 40 metros ha participado en numerosos proyectos de gran interés científico, tanto de carácter nacional como internacional. Algunos de los proyectos en los que se ve inmerso en la actualidad son: RADIONET (BRAND, AETHRA y TOG), ALMA, IRAM (NOEMA), NANOCOSMOS, SKA y JUMPING JIVE.

Figura 4: Radiotelescopio de 40 metros del Observatorio de Yebes [15].

Por último, cabe destacar que el desarrollo histórico ha tendido hacia la obtención de una mayor sensibilidad, una longitud de onda más corta y una mayor resolución angular en las observaciones.

#### 2.1.2 Gestión del espectro en radioastronomía

La gestión del espectro es un conjunto de procedimientos administrativos y técnicos que tienen como fin una correcta asignación del espectro de radiofrecuencia. El espectro es un bien limitado y gestionado por el estado.

En el caso de la radioastronomía, se trata de un servicio de radio pasivo cuyo objetivo principal es la búsqueda y recepción de señales con niveles de potencia muy bajos. Este contexto hace que este tipo de servicio de radio sea especialmente vulnerable a posibles interferencias generadas por otros servicios de radio activos. Dichas interferencias son provocadas, principalmente, por servicios que comparten la misma banda de frecuencia, pero también pueden ser generados a partir de transmisiones que no pertenecen a la misma banda.

El reconocimiento de la radioastronomía como un servicio de radio de importancia pareja a la de otros servicios, como el de las comunicaciones móviles, supuso la creación de una base legal que brinda de protección frente a interferencias perjudiciales para las observaciones. Dicha protección se obtiene a través del establecimiento de zonas de coordinación para los servicios terrestres. En estas zonas de coordinación se garantiza que las transmisiones ajenas a fines radioastronómicos no generen interferencias perjudiciales.

Las bandas dedicadas a la radioastronomía en la región Europa, Asia y África son las siguientes:

- Bandas de 37.5 a 38 MHz y de 38 a 38.25 MHz: Bandas atribuidas globalmente a la radioastronomía con atribuciones secundaria y primaria, respectivamente. Estas bandas son compartidas con servicios fijos y móviles.

- Banda de 406.1 a 410 MHz: Esta banda es una de las más utilizadas en observaciones radioastronómicas continuas. Dispone de atribución primaria compartida con los servicios fijo y móvil.

- Banda de 1400 a 1427 MHz: Muy importante para los estudios de la línea de hidrógeno y la naturaleza de las galaxias. Dispone de atribución primaria compartida con el servicio de exploración de la Tierra por satélite y el servicio de investigación espacial.

- Bandas de 1610.6 a 1613.8 MHz y 1660 a 1670 MHz: Bandas muy utilizadas para realizar observaciones de las líneas espectrales del radical hidrógeno e hidroxilo, las cuales son de vital importancia por su amplia distribución en el universo. Esta distribución permite llevar a cabo estudios sobre la naturaleza y evolución del mismo universo. Dichas bandas comparten categoría primaria con los servicios de móvil por satélite, radionavegación aeronáutica, servicios de investigación espacial y con el servicio de ayudas a la meteorología. Estos servicios con los que comparte banda dificultan mucho las observaciones en este rango de frecuencias.

- Banda de 2690 a 2700 MHz: Banda de vital importancia para la observación astronómica debido a su baja radiación de fondo galáctico y su gran productividad a la hora de realizar estudios de las nubes de hidrógeno ionizado, y de la radiación difusa general de la galaxia. Esta banda dispone de atribución primaria, y está compartida con el servicio de exploración de la Tierra por satélite y el servicio de investigación espacial.

- Bandas de 4800 a 4990 MHz y de 4990 a 5000 MHz: Estas bandas de frecuencia son utilizadas para los estudios de distribuciones de brillo de objetos galácticos tales como, nubes de hidrógeno ionizado y remanentes de supernovas. Las bandas de frecuencia en cuestión disponen de atribuciones secundaria y primaria, respectivamente, y se encuentran compartidas con servicios fijo y móvil.

- Banda 10.68 a 10.7 GHz: Banda con título primario compartida para usos de radioastronomía, exploración de la Tierra por satélite e investigación espacial. Es una de las bandas más utilizadas para observaciones continuas.

- Banda de 14.47 a 14.5 GHz: Esta banda ha sido determinada por los radioastrónomos como una de las más importantes a frecuencias por debajo de 275 GHz. Tanto es así que se solicita a los servicios fijos y móviles que no asignen frecuencias en esta banda.

- Banda de 15.35 a 15.4 GHz: Otra de las bandas predilectas de los radioastrónomos para la realización de observaciones continuas. Esta banda también se encuentra compartida con servicios de exploración de la Tierra por satélite e investigación espacial.

- Banda de 22.21 a 22.5 GHz: Esta banda está definida por los radioastrónomos como "la banda preferida" para la realización observaciones continuas. También dispone de atribución primaria y es compartida con los servicios fijo, móvil, exploración de la Tierra por satélite e investigación espacial.

- Banda de 23.6 a 24 GHz: Está banda es la primaria en servicios de radiocomunicaciones pasivos, es decir, servicios de radioastronomía, exploración de la Tierra por satélite y servicios de investigación espacial.

- Bandas por encima de 40 GHz: Existen bandas de frecuencias superiores a 40 GHz destinadas a la radioastronomía, pero las interferencias generadas por otros servicios activos en estos rangos son mínimas, por lo que no suelen suponer un problema. En cuanto a las observaciones que se llevan a cabo, son de carácter continuo o de líneas espectrales.

Una vez expuestas las bandas frecuenciales del espectro radioeléctrico más relevantes para uso radioastronómico, es menester contextualizar estos rangos frecuenciales para el caso que no ocupa. El observatorio de Yebes dispone de un radiotelescopio de 40 m con el que se pueden llevar a cabo observaciones de antena única y de VLBI, que se llevan a cabo en conjunto con otros radiotelescopios, este concepto será expuesto más adelante con más detalle. Las bandas de frecuencia con las que se realizan las observaciones difieren si son de antena única o de VLBI.

Para el caso de antena única las tres bandas de frecuencia fundamentales son: 18-26 GHz, 32-50 GHz y 72-90 GHz. Las restantes se encuentran en rangos superiores a los 40 GHz, estas bandas son muy selectas ya que no hay demasiados sistemas en la actualidad capaces de operar a tan altas frecuencias.

En cuanto a las observaciones VLBI, el Observatorio de Yebes colabora con redes tales como la red europea de VLBI EVN, la red VLBI milimétrica GMVA, la red geodésica International VLBI Service y otras redes como KaVa y Radioastron.

#### 2.2 El radiotelescopio

El elemento fundamental en toda observación radioastronómica es el radiotelescopio, cuya función principal es captar la energía emitida por una fuente cósmica con una antena parabólica. Dichas señales de energía tienen niveles de potencia muy bajos debido a las grandes distancias a las que se encuentran. El tamaño de la parábola de la antena debe ser grande para captar dichas señales, y depende de la frecuencia de funcionamiento.

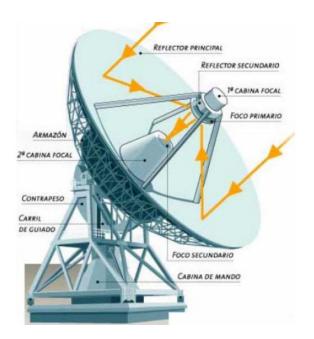

En cuanto al funcionamiento, la energía que llega se concentra en el foco, donde se encuentra el receptor. La energía llega a través de una onda plana en la dirección del eje óptico mediante reflexión, generándose un diagrama de difracción centrado en el citado eje óptico. La Figura 5 muestra las partes de un radiotelescopio.

Figura 5: Partes del radiotelescopio (extraída de http://giomepe1214.blogspot.com/2017/09/radiotelescopio.html).

Como se ha indicado anteriormente, para captar señales de manera óptima se deben utilizar grandes antenas o grupos de antenas trabajando en paralelo (array), esto permite observar el espectro radioeléctrico de una parte del cielo. Pero el tamaño de la antena no se ve solo motivado por la capacidad de captación de energía, sino también por la resolución. La resolución del radiotelescopio es la distancia angular que existe entre dos puntos para que puedan ser identificados por separado, y es un parámetro esencial a la hora de diseñar un radiotelescopio.

La antena solo constituye el primer elemento del radiotelescopio, esta va seguida de un receptor y un sistema de procesamiento con el que se lleva a cabo el tratamiento de la señal captada. En la Figura 6 se muestra el esquema básico de un radiotelescopio.

Figura 6: Diagrama de bloques de un radiotelescopio.

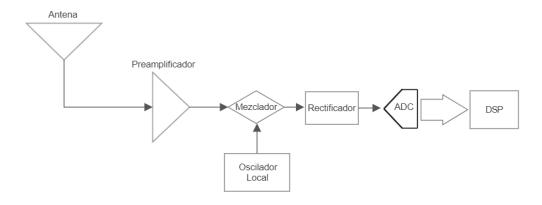

#### 2.3 El receptor radioastronómico

Como se ha indicado antes, la energía que es capaz de captar la antena del radiotelescopio se concentra en el foco, donde se encuentra el receptor. Un receptor de radioastronomía es un elemento que se encarga de transformar correctamente la energía captada por la antena. Dichas señales de energía suelen tener niveles de potencia muy bajos, por lo que es necesario amplificarlas adecuadamente en la etapa de recepción. Además, se llevan a cabo procesamientos en las señales tales como conversión a otro rango de frecuencias o filtrado de las mismas que permiten adaptar la señal a las necesidades del backend. Además, si se llevan a cabo técnicas de interferometría se deben añadir señales de calibración y medida de tiempo, con el fin de sincronizar con otros radiotelescopios de la red. Para llevar a cabo todo el tratamiento de señal el receptor dispone de las siguientes partes:

- Criostato: Es el primer elemento que conforma la cadena de recepción de la señal, está compuesto por una bocina y amplificador de bajo ruido que se encuentran a temperaturas inferiores a los 260º bajo cero. La motivación principal de esta etapa del receptor, es que este sea lo más sensible posible, para lo cual sus elementos deben generar muy poco ruido electrónico. Esto se consigue enfriando por vacío criogénico la etapa más crítica del sistema a la temperatura especificada anteriormente.

- Conversores de frecuencia: Su uso es fundamental debido a la dificultad a la hora de procesar señales de muy alta frecuencia. Permiten convertir la señal que proviene del criostato a frecuencias más bajas mezclando la señal de la antena con una proveniente de un oscilador local. Con estas dos señales se genera una señal de frecuencia intermedia, la cual debe ser correctamente filtrada para evitar banda imagen y amplificada para adaptar su potencia a las necesidades del backend. Con esto se consigue reducir la frecuencia de la señal y adaptar su potencia a las necesidades del backend.

- Backend: Es el último elemento de la cadena receptora y su función es procesar las señales provenientes de la etapa anterior. Los backends de radioastronomía generalmente constan de una primera etapa de digitalización de los datos, seguida de un generador de transformada de Fourier. Este es el elemento en el que se va a centrar este TFG, y se ha optado por hacer uso de FPGAs para su desarrollo. El uso de FPGAs cada vez está más extendido en radioastronomía debido a su gran velocidad de procesamiento, baja potencia y flexibilidad de cara a reprogramar diferentes distribuciones hardware.

#### 2.4 VLBI

Las siglas VLBI significan en castellano "Interferometría de muy larga línea de base" [2]. Se trata de una técnica utilizada en radioastronomía que consiste en combinar señales de múltiples radiotelescopios, separados por distancias muy grandes, para crear un telescopio virtual con un tamaño igual a la separación máxima entre los radiotelescopios.

Al combinar las señales de múltiples telescopios, VLBI puede lograr una resolución angular extremadamente alta, lo que permite a los astrónomos estudiar los detalles finos de los objetos celestes con gran precisión. Cada uno de los radiotelescopios recibirá la radiación emitida por el citado objeto en instantes de tiempo distintos, generando un patrón de interferencia denominado franja. Esto permite a la red comportarse como un único instrumento de un tamaño equivalente igual a la distancia entre radiotelescopios [4]. VLBI se utiliza para estudiar una amplia gama de fenómenos astronómicos, incluidos los agujeros negros, los cuásares y la estructura de la galaxia de la Vía Láctea.

Las señales recibidas por cada antena del array están sincronizadas con un reloj atómico de Hidrógeno de altísima precisión, el máser de hidrógeno. A continuación, dichos datos son enviados al correlador por un enlace de fibra óptica. El correlador es un computador cuyo objetivo es captar los datos de todas las antenas del array y multiplicarlos, generando así una imagen en 2-D de la región del cielo observada. La resolución obtenida es proporcional a la frecuencia de observación. Las técnicas de VLBI permiten que la distancia entre telescopios sea mucho más grande que las posibles con la interferometría tradicional. Esta última hacia uso de antenas conectadas con cable coaxial, guía de onda o fibra óptica, debido a que no existe la pérdida de potencia que genera el transporte de la señal por un medio físico.

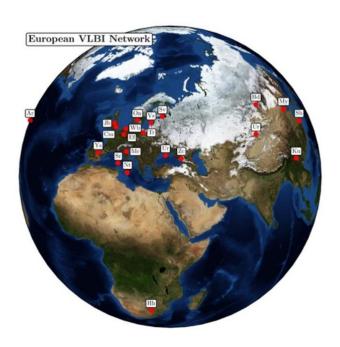

El array más grande de interferometría existente en el mundo es La red europea de VLBI (EVN) es el array de interferometría más grande actualmente. Dispone de 21 radiotelescopios extendidos por toda Europa que observan en tres periodos por año, dichos periodos se conocen como Sesiones VLBI. La ubicación de dichos radiotelescopios se muestra en la Figura 7.

Figura 7: Posición de los radiotelescopios de la red europea de VLBI [15].

#### 2.5 Ocultaciones lunares

Una ocultación es la alineación o interposición de un cuerpo celeste por otro visto desde la Tierra. Dependiendo del tipo de trayectoria o paso entre ambos objetos, estos eventos pueden ser:

- Totales y anulares: si se produce la desaparición o superposición completa.

- Parciales: si únicamente se tapa una parte.

- Rasante: si el paso se produce tangencialmente.

La Figura 8 muestra una representación gráfica de los eventos anteriormente descritos.

Figura 8: Tipos de ocultaciones según la alineación de los cuerpos entre los que tiene lugar el fenómeno [5].

La diferencia entre los tamaños aparentes (o vistos desde la Tierra) del cuerpo ocultante y del ocultado establecen diferentes tipos de fenómenos:

- Eclipses: cuando las dimensiones aparentes de ambos objetos son similares.

- Tránsitos: cuando el cuerpo ocultante es mucho más pequeño que el ocultado. En tal caso no se produce la desaparición del cuerpo más distante, sino un paso o tránsito del primero proyectado sobre la superficie del mayor.

- Ocultaciones: cuando el cuerpo que causa el fenómeno es mucho mayor aparentemente que el ocultado.

El foco de interés de este proyecto hay que ponerlo en las ocultaciones lunares. Un ejemplo típico son las ocultaciones de estrellas por la Luna, las estrellas son mucho mayores que nuestro satélite, pero sus tamaños aparentes son muy dispares desde nuestra perspectiva y se ven ocultadas.

Las ocultaciones han sido fuente de importantes descubrimientos en la Astronomía, tales como la determinación de la distancia Tierra-Sol, los tamaños y formas de los asteroides, la atmósfera de Plutón o la localización precisa de algunas radiofuentes [5].

#### 2.6 FPGAs

A comienzos de la década de 1980 se hizo notoria la demanda de nuevos dispositivos programables. En un extremo se encontraban los PLD (Dispositivos Lógicos Programables), altamente configurables, pero no capaces de soportar funciones complejas. En el otro extremo se encontraban los ASIC, que sí soportaban funciones complejas pero su diseño era muy costoso y laborioso. Además, los ASIC no son reconfigurables debido a que se congelan en silicio una vez implementados.

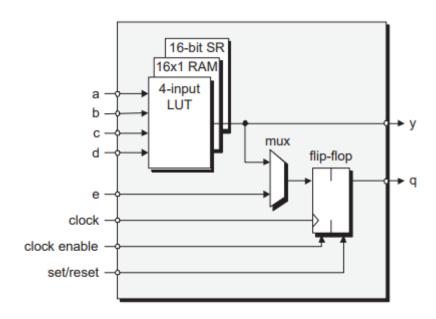

En este contexto, y con el fin de paliar esta demanda, Xilinx desarrolló un nuevo tipo de dispositivo programable llamado FPGA (Field-Programmable Gate Array). La arquitectura de las primeras FPGA, aparece representada en la Figura 9, y se basaba en el concepto de un bloque lógico programable (CLB) que comprendía una LUT (tabla de búsqueda) de tres entradas, un flip-flop y un multiplexor [14].

Figura 9: Diagrama de bloques de los primeros CLB [14].

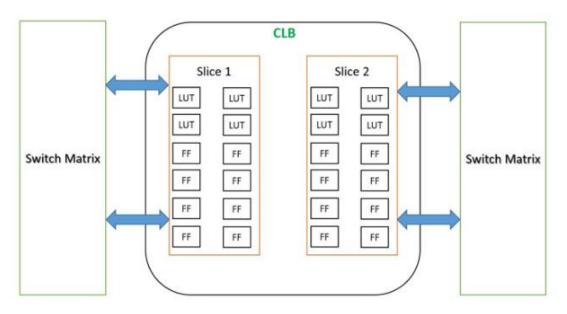

La arquitectura de la parte programable del dispositivo que nos ocupa es de una complejidad mayor a la descrita anteriormente, pero la estructura básica se mantiene. La lógica programable del Zynq SoC consta de bloques lógicos configurables (CLB), cada uno de los cuales contiene dos segmentos. Cada segmento contiene cuatro tablas de búsqueda (LUT), ocho flip-flops (FF) y una matriz de conmutación que lo acompaña. La Figura 10 muestra el diagrama de bloques de un CLB.

Figura 10: Arquitectura de un CLB (extraída dehttps://www.aldec.com/en/company/blog/144--introduction-to-zynq-architecture).

A continuación, se exponen con más detalle las partes del CLB:

- Slice: Pequeña unidad de lógica dentro de la estructura FPGA que se puede configurar para realizar varias funciones lógicas digitales, tales como implementar circuitos combinacionales y secuenciales.

- Tabla de búsqueda (LUT): Es un circuito digital que se puede configurar para implementar una función booleana de seis entradas. La salida de una LUT está determinada por una tabla de verdad, que es una lista de todas las combinaciones de entrada posibles y sus correspondientes salidas. Una LUT se puede utilizar para implementar lógica combinacional, como puertas AND, OR y NOT, así como funciones booleanas más complejas, como sumadores, comparadores y máquinas de estado.

- Flip-flop (FF): Es un elemento de memoria que puede almacenar un solo bit de información y puede usarse para implementar lógica secuencial. En la arquitectura Zynq se emplea para almacenar la salida de una LUT y ponerla a disposición de otras partes del diseño. También se pueden usar para implementar una lógica secuencial más compleja, como contadores, máquinas de estado y elementos de memoria.

- Matriz de conmutación: Es una red de recursos de enrutamiento programables que permite interconectar señales entre diferentes partes del diseño, como entre segmentos dentro de un CLB, entre los mismos CLB o entre la estructura FPGA y el procesador o las interfaces.

#### 2.7 Uso de FPGAs en radioastronomía

El uso de las FPGAs está muy extendido en aplicaciones de radioastronomía para procesar y analizar las grandes cantidades de datos que suministran los radiotelescopios.

Una de las principales aplicaciones que se les otorga a estos dispositivos es el desarrollo de backends digitales para los radiotelescopios. Un backend digital es un sistema que digitaliza y procesa señales de datos. Las FPGAs resultan interesantes para este tipo de sistemas porque pueden ser programadas para llevar a cabo multitud de tareas de procesamiento de señal en tiempo real. Además, son muy útiles en el desarrollo de algoritmos de procesamiento digital de señal que puedan ser implementados en el hardware.

Las FPGAs se usan también en otros sistemas como conformadores de haz, en los cuales se combinan señales provenientes de múltiples antenas para crear una única con alta resolución. Son ideales para este tipo de sistemas ya que pueden llevar a cabo funciones de correlación en tiempo real.

En resumen, el uso de FPGAs está muy extendido en el campo de la radioastronomía para procesar y analizar grandes cantidades de datos. Pueden ser usados para el desarrollo de backends digitales, conformadores de haz y radiotelescopios de baja frecuencia, debido a su adaptabilidad y a sus capacidades de procesamiento en tiempo real y de implementación de algoritmos de procesamiento digital de señales.

#### 2.8 Observatorio de Yebes

El Observatorio de Yebes constituye actualmente un Centro de Desarrollo Tecnológico para el Instituto Geográfico Nacional (IGN) siendo uno de los diez centros de investigación científica totalmente españoles clasificados como Gran Instalación Científica. Está dedicado al desarrollo y construcción de instrumentación en el campo de la radioastronomía, así como a la realización de observaciones astronómicas tanto de interés astronómico como geodésico o geofísico.

El Observatorio forma parte de infinidad de proyectos con empresas o instituciones internacionales para el desarrollo de receptores de radioastronomía en diferentes bandas. También participa en el desarrollo y fabricación de amplificadores criogénicos ultrasensibles. Dichos amplificadores son usados en los receptores de los radiotelescopios de la institución.

Los receptores desarrollados por el laboratorio del Observatorio son los siguientes:

Banda S: 2.2 - 2.37 GHz

Banda CH: 3.22 - 3.39 GHz.

- Banda C: 4.56 - 6.9 GHz

- Banda X: 8.1 - 8.9 GHz

- Banda K: 21 - 24 GHz

Banda Q: 31.5 - 50 GHz

Banda W: 72-90.5 GHz y 83-116 GHz.

- Tri-banda: S (2.2-2.7GHz) / X (7.5-9 GHz) / Ka (28-33 GHz) tres bandas simultáneas

Banda ancha VGOS: 2-14 GHz.

Además, el Observatorio participa en proyectos de carácter nacional e internacional para la creación de nuevos tipos de receptores. En este plano, el Observatorio pretende desarrollar de manera autónoma sus backends de recepción, para lo cual la opción más factible es hacer uso de system on chip basado en FPGA, debido a su gran flexibilidad en cuanto a frecuencias de recepción se refiere.

El radiotelescopio de 40 m es uno de los nodos más importantes de la Red Europea de Interferometría de Muy Larga Base, una de las mayores instalaciones científicas del mundo, y es una estación del Servicio Internacional de VLBI para Geodesia y Astrometría.

# Capítulo 3: Descripción del hardware e introducción al desarrollo de un sistema basado en Zynq

En el presente capítulo se expondrán en detalle las características del hardware empleado, así como los procedimientos a llevar a cabo de cara al desarrollo de un diseño basado en el citado hardware.

Para el desarrollo del diseño se ha optado por emplear la tarjeta de desarrollo Zedboard, un SoC basado en FPGA de la familia Zynq de Xilinx. Este tipo de dispositivo consta de dos bloques principales: El Processing System o PS y la Programmable Logic o PL. Ambos bloques se interconectan mediante enlaces AXI (Advanced eXtensible Interface). Mientras que la lógica programable provee de funcionalidades como lógica de alta velocidad u operaciones aritméticas, el sistema de procesamiento proporciona soporte para la ejecución de rutinas software y/o sistemas operativos. La Figura 11 muestra un modelo simplificado de la arquitectura.

Figura 11: Modelo simplificado de la arquitectura Zynq [7].

Para la digitalización de los datos se hará uso de la tarjeta AD9467-FMC-250EBZ basada en el conversor analógico digital AD9467, que se conecta a la Zedboard por medio del puerto FMC de la misma.

Para llevar a cabo el desarrollo de un sistema basado en Zynq es preciso realizar un diseño dual, es decir, primero se debe abordar el desarrollo hardware y después el desarrollo software.

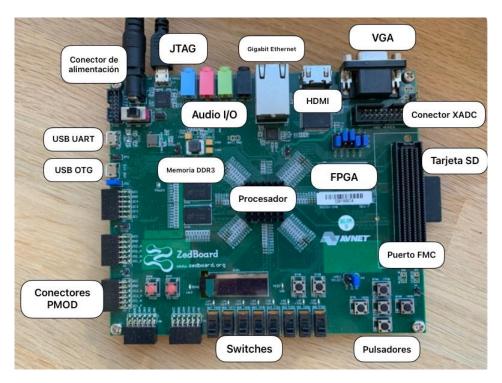

# 3.1 Tarjeta de desarrollo Zedboard

ZedBoard es una placa de evaluación y desarrollo basada en Xilinx Zynq-7000 All Programable SoC (AP SoC). Combina un sistema de procesamiento dual Cortex-A9 (PS) con 85.000 celdas de lógica programable (PL) de la serie 7 de Xilinx [6].

La placa proporciona una amplia gama de interfaces y periféricos tales como USB, Ethernet, HDMI e interfaces de tarjeta SD, que se pueden conectar a la FPGA mediante la interconexión programable que esta ofrece. Esto permite el desarrollo de infinidad de aplicaciones y sistemas integrados. Además, ZedBoard está diseñado para ser compatible con una amplia gama de herramientas de desarrollo de software, como Xilinx Vivado y PetaLinux, que pueden ser empleados para crear diseños personalizados para la placa.

# 3.1.1 Sistema de procesamiento (PS)

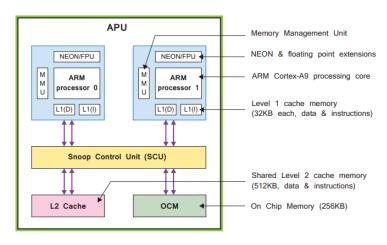

ZedBoard incluye un sistema de procesamiento (PS) que combina un procesador ARM Cortex-A9 de doble núcleo con una amplia gama de interfaces periféricas. El sistema de procesamiento está conformado principalmente por la APU (Application Processor Unit), la memoria caché, memoria ROM y RAM, interfaces para memoria externa, controlador DMA y diferentes periféricos e interfaces de entrada/salida.

El procesador ARM Cortex-A9 de doble núcleo de ZedBoard es un procesador de 32 bits que funciona a una frecuencia de reloj de 800 MHz. Es la piedra angular de la APU y se basa en la arquitectura ARMv7-A. Además, la sección PS del dispositivo Zynq incluye una caché de Nivel 1 (L1) y una caché de Nivel 2 (L2). Cada uno de los cores dispone de sus propias cachés independientes de primer nivel (L1) para código y datos, siendo cada una de ellas de 16KB. La caché L2 es de 512 KB, con uso compartido para el almacenamiento de datos e instrucciones. Incluye también una "On-Chip" RAM de 256 KB destinada a almacenamiento de datos. La Figura 12 muestra la arquitectura de la APU.

Figura 12: Diagrama de bloques de la APU.

El sistema de procesamiento también incluye una amplia gama de interfaces y periféricos que pueden ser empleados para establecer conexiones con dispositivos externos. Algunas de estas interfaces son USB, Gigabit Ethernet, HDMI, tarjeta SD y UART, entre otras. Además, se pueden conectar a la FPGA mediante la interconexión programable, lo que permite que la FPGA se comunique con los periféricos y realice las tareas de procesamiento necesarias. La citada interconexión se lleva a cabo con una arquitectura de buses denominada AXI, desarrollada por ARM y que será expuesta más adelante en el capítulo.

Además, el sistema de procesamiento incluye un controlador de memoria DDR3, que puede usarse para conectarse a una memoria externa. Esta memoria se puede utilizar para almacenar o acceder a datos para el procesador y la FPGA. Dispone también de un controlador DMA (Direct Memory Access) de ocho canales, encargado de agilizar los accesos a memoria.

# 3.1.2 Lógica Programable (PL)

La lógica programable en ZedBoard es proporcionada por el FPGA Xilinx Zynq-7000. Más en concreto, hace uso del dispositivo Z-7020, cuya FPGA Artix-7 consta de 85000 celdas lógicas, 53200 LUTs, 106400 biestables, 4,9 Mb de RAM y 220 DSP Slices. Estos se pueden programar para realizar funciones lógicas digitales, tales como puertas lógicas, contadores y máquinas de estado. La interconexión programable se compone de una gran cantidad de puntos de interconexión programables (PIP), que se pueden usar para conectar los bloques CLB y DSP, y así crear circuitos lógicos personalizados.

La lógica programable también incluye un módulo formado por dos ADCs de 12 bits (XADC), con el que se pueden digitalizar tanto entradas externas como parámetros internos de la placa referentes a medidas de temperatura o voltaje.

# 3.2 Periféricos en Zynq

La tarjeta de desarrollo Zedboard incluye un dispositivo Zynq ZC7Z020, basado en la estructura lógica Artix-7. Éste presenta los siguientes dispositivos:

- Lógica Programable (PL): Es usada para enlazar el dispositivo Zynq con interfaces, customizadas o existentes, y así dotarlo de la funcionalidad que estos aporten.

- Controlador de memoria DDR: Se trata de un controlador de memoria que aparece integrado en dispositivos Xilinx Zynq-7000 AP SoC (All Programmable System on Chip). Éste es el responsable de administrar el flujo de datos entre los núcleos del procesador y la memoria DDR externa, dando soporte a los estándares de memoria de tipo DDR2 y DDR3. La Zedboard tiene una sola ranura de memoria DDR3 y admite una capacidad máxima de memoria de 1GB. Dicha memoria está conectada al AP SoC por medio de una interfaz de 32 bit.

- Gigabit Ethernet: Es un controlador Ethernet de alta velocidad que permite que el dispositivo Zynq establezca comunicaciones con otros dispositivos en la red. Da soporte al estándar IEEE 802.3 para Gigabit Ethernet y puede manejar tasas de transferencia de 10, 100 y 1000 Mbps. También incluye características tales como corrección de errores y control de flujo, y puede ser configurado para operar en modo MII (Media Independent Interface) o GMII (Gigabit Media Independent Interface), que básicamente determinará el número de pines que se va a usar para establecer la conexión con el Ehernet PHY (Physical Layer).

- USB 2.0 (Universal Serial Bus): Se trata de un controlador de interfaz de altas prestaciones que habilita conexiones del dispositivo Zynq con dispositivos USB. El controlador USB 2.0 puede manejar tasas de transferencia de hasta 480 Mbps y da soporte a los modos de operación: USB servidor, dispositivo USB y OTG (On The Go), que es un híbrido de los dos anteriores.

- SD/SDIO (Secure Digital/Secure Digital Input Output): Un controlador de periféricos que habilita al dispositivo Zynq a establecer conexiones con tarjetas SD y SDIO. Permite manejar tasas de transferencia de hasta 48 Mbps.

- General Purpose Input/Output (GPIO): El dispositivo Zynq incluye cuatro bancos de 32 pines cada uno que pueden ser configurados como entrada o salida, y cuyo nivel de voltaje puede ser modificado individualmente. Los bancos 0 y 1 están asociados a la interfaz MIO, mientras que los bancos 2 y 3 están asociados a la interfaz EMIO.

- Universal Asynchronous Receiver-Transmitter (UART): El módulo UART del dispositivo Zynq es un canal de comunicación full-duplex asíncrono que puede operar con tasas de transferencia de hasta 3 Mbps. Incluye un transmisor y un receptor, cada uno de los cuales posee un búfer FIFO (First In First Out). Además, incluye varias características como control de flujo, paridad y longitud de palabra de datos variable.

- Inter-Integrated Circuit (I2C): Este controlador es un módulo que permite establecer comunicaciones entre el procesador y otros dispositivos haciendo uso del protocolo I2C.

- Serial Peripheral Interface (SPI): El controlador SPI del dispositivo Zynq puede ser configurado por software, y posee múltiples líneas SS (Slave Select) para permitir comunicaciones con múltiples dispositivos simultáneamente.

- Direct Memory Access (DMA): El controlador DMA permite que el dispositivo Zynq realice transferencias de alta velocidad entre los periféricos y la memoria sin hacer uso del procesador. Ofrece la posibilidad de operar en modo scatter/gather, en el cual los datos son transferidos a múltiples direcciones de memoria desde un periférico, o viceversa. Además, el controlador DMA puede ser configurado para hacer uso del protocolo AXI, que permite realizar transferencias de datos a alta velocidad conectándose con otros módulos con compatibilidad AXI del diseño.

# 3.3 Conexiones en 7edboard

Zedboard incluye una gran variedad de interfaces y conectores para enlazar dispositivos externos y periféricos, los cuales aparecen ilustrados en la Figura 13:

Figura 13: Partes de la Zedboard.

- USB-UART (Universal Asynchronous Receiver/Transmitter): El puente USB-UART convierte los datos enviados a través de USB al protocolo UART, que pueden ser leídos por medio del controlador UART de ZedBoard. Esto permite una fácil comunicación con la placa utilizando un programa de terminal serie estándar en un host.

- USB OTG (On The Go): Es una especificación que permite que un dispositivo USB actúe como host y como dispositivo. Su utilidad es que permite que la Zedboard se comunique con otros dispositivos USB sin necesidad de un ordenador host adicional. Utiliza un conector USB micro-AB que admite los modos de host USB y dispositivo USB. Cuando la ZedBoard está configurada como host puede comunicarse con otros dispositivos USB, como una memoria USB. Mientras que, cuando está configurada como USB, puede conectarse a un ordenador host y ser reconocida como un dispositivo convencional. La interfaz USB OTG en Zedboard está monitorizada por el controlador USB integrado, que forma parte del PS.

- Gigabit Ethernet: Permite que la tarjeta se conecte a una red y se comunique con otros dispositivos a altas velocidades. Está monitorizada por el controlador de acceso a medios (MAC) Ethernet. El MAC es el responsable de controlar el flujo de datos hacia y desde la interfaz Ethernet, así como de realizar la verificación y corrección de errores. La interfaz utiliza un conector RJ-45, que es compatible con cables Ethernet estándar. Además de la conexión física, Zedboard también tiene la capacidad de ejecutar la pila TCP/IP y otros protocolos de red, lo que le permite conectarse a varias redes y también realizar varias funciones de red como DHCP, servidor web, servidor FTP, etc.

- VGA: La interfaz VGA permite que ZedBoard emita datos de vídeo a un monitor o pantalla VGA. Está monitorizado por el controlador VGA integrado, que es responsable de codificar y decodificar los datos de vídeo que se envían y reciben desde la interfaz VGA. Esta utiliza un conector VGA estándar, que es compatible con la mayoría de los cables y pantallas VGA.

- HDMI (High-Definition Multimedia Interface): Es una interfaz digital destinada a la transmisión de vídeo y audio de alta definición. La interfaz HDMI en ZedBoard está controlada por el controlador HDMI integrado. Este es el responsable de codificar y decodificar los datos de vídeo y audio que se envían y reciben desde la interfaz. Además, utiliza un conector HDMI tipo A estándar, que es compatible con la mayoría de los cables y pantallas HDMI.

- Audio: La interfaz de audio permite que ZedBoard capture y transmita señales de audio a dispositivos externos, como micrófonos o auriculares. La interfaz de audio está controlada por el códec de audio incorporado, que es un chip separado en la placa. Este es el responsable de convertir los datos de audio digital en señales de audio analógicas, y viceversa. Por último, utiliza un conector de 3,5 mm para la salida de audio y una entrada de micrófono.

- SD Card: La interfaz de la tarjeta SD permite que ZedBoard lea y escriba datos en una tarjeta SD, que se puede usar para almacenamiento o como medio de arranque. Esta interfaz está monitorizada por el controlador SD incorporado, el cual es responsable de leer y escribir datos en la tarjeta SD, así como de administrar el flujo de datos y realizar la verificación y corrección de errores. Utiliza una ranura para tarjeta SD estándar, que es compatible con la mayoría de las tarjetas SD.

- JTAG (Joint Test Action Group): Es una interfaz estándar de depuración y programación que permite establecer una comunicación entre ZedBoard y un host. JTAG se utiliza para programar la memoria flash integrada, depurar el software que se ejecuta en la placa y acceder a los registros internos de la placa. Utiliza una interfaz de 4 o 5 cables para establecer la conexión, generalmente a través de un adaptador JTAG o un programador USB-JTAG. La interfaz JTAG en ZedBoard está monitorizada por el controlador JTAG integrado.

- PMOD (Peripheral Module): Es una interfaz estándar que permite la conexión de dispositivos periféricos a la placa a través de un conector de 6 o 12 pines. La interfaz PMOD está controlada por la lógica programable integrada y el procesador del SoC.

- Conectores de alimentación: La placa incluye conectores de alimentación que proporcionan la energía necesaria para que funcione la placa. Estos conectores permiten la conexión de fuentes de alimentación externas a la ZedBoard e incluyen un conector de alimentación de DC, que permite una conexión de una fuente externa de 12 V, y un interruptor de alimentación, para encender y apagar el dispositivo.

- Conector XADC: Permite la conexión de señales analógicas externas. El conector XADC en ZedBoard brinda acceso al módulo XADC en el chip, que es un conversor analógico digital de 1 MSPS y 12 bits. El XADC se puede usar para monitorizar varios voltajes integrados, como el voltaje de alimentación y la temperatura del SoC.

- Conector FMC (FPGA Mezzanine Card): Interfaz que permite al usuario conectar una gran variedad de tarjetas secundarias FMC a Zedboard. Estas pueden proporcionar funcionalidades adicionales a la placa. Pueden ser conversores analógico digitales, conversores digital analógicos y otros dispositivos periféricos. El conector FMC cumple con el estándar VITA 57.1, que define las especificaciones mecánicas y eléctricas de las tarjetas FMC. Esto permite utilizar una amplia gama de tarjetas FMC de terceros con la placa.

# 3.4 Protocolo AXI

El protocolo AXI define un conjunto de señales que se utilizan para la comunicación entre los componentes del diseño de un SoC. Estas señales se pueden agrupar en tres categorías principales:

- Señales de transferencia de datos: Estas señales se utilizan para la transferencia de datos entre los componentes. El protocolo AXI define canales separados para operaciones de lectura y escritura, lo que permite la transferencia simultánea de datos. Las señales de transferencia de datos incluyen:

- AWADDR: Señal con la dirección para operaciones de escritura.

- WDATA: Señal de datos para operaciones de escritura.

- BRESP: Señal de respuesta para operaciones de lectura.

- ARADDR: Señal que porta la dirección para operaciones de lectura.

- RDATA: Señal de datos para operaciones de lectura.

- Señales de control: estas señales se utilizan para controlar el flujo de transferencia de datos. Las señales de control incluyen:

- AWVALID: Indica que hay una dirección de escritura y datos válidos disponibles.

- AWREADY: Indica que el componente está listo para aceptar una dirección de escritura y datos.

- WVALID: Indica que hay datos de escritura válidos disponibles.

- WREADY: Indica que el componente está listo para aceptar datos de escritura.

- BVALID: Indica que hay disponible una respuesta de lectura válida.

- BREADY: Indica que el componente está listo para aceptar una respuesta de lectura.

- ARVALID: Indica que hay disponible una dirección de lectura válida.

- ARREADY: Indica que el componente está listo para aceptar una dirección de lectura.

- Señales de gestión: Estas señales se utilizan para gestionar la comunicación entre componentes. Las señales de gestión incluyen:

- ACK: Señal de acuse de recibo.

- INTERRUPT: Señal de interrupción.

RETRY: Señal de reintento.

En cuanto a la teoría de operación, el componente maestro inicia una transferencia activando la señal de control adecuada (AWVALID o ARVALID) y proporcionando la información necesaria (dirección y datos) en las líneas de señal correspondientes. El componente esclavo responde activando la señal de control adecuada (AWREADY o ARREADY) para indicar que está listo para aceptar la transferencia. Una vez que se completa la transferencia, el componente esclavo afirma la señal de respuesta adecuada (BRESP o RDATA) para indicar el estado de la transferencia. Luego, el componente maestro acusa recibo de la finalización de la transferencia anulando la señal de control apropiada.

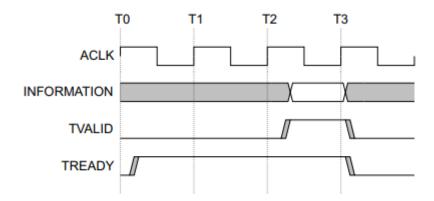

## 3.4.1 AXI4-Stream

AXI4-Stream es un protocolo diseñado para transportar datos unidireccionalmente de manera arbitraria. El protocolo AXI4-Stream puede utilizar hasta 11 señales, algunas de ellas opcionales. Para este proyecto se utilizarán únicamente 6 señales, una de ellas opcional.

- ACLK: La señal de reloj global. Todas las señales se muestrean en el flanco ascendente de ACLK.

- ARESETn: La señal de reinicio global. ARESETn es activa a nivel bajo.

- TVALID: Procedente del lado maestro. Indica que el maestro está generando una transferencia válida.

- TREADY: Procedente del esclavo. Indica que el esclavo puede aceptar una transferencia en el ciclo actual. Una transferencia solo tiene lugar cuando tanto TVALID como TREADY se afirman.

- TDATA: Procedente del maestro. Es la carga útil principal que se utiliza para proporcionar los datos que pasan a través de la interfaz.

- TLAST: Procedente del maestro. Se utiliza para dividir los datos transferidos en paquetes. Cuando está activo, indica el final de un paquete.

En un AXI4-Stream, los bits contenidos en la señal TDATA se transfieren cada ciclo de reloj. La transferencia se inicia cuando el emisor envía la señal TVALID y el receptor responde enviando la señal TREADY. En este punto, el emisor comenzará a enviar TDATA y TLAST. TLAST señala el último byte del paquete, por lo que el receptor seguirá aceptando el contenido de TDATA hasta que se afirme la señal TLAST [8].

Figura 14: Ejemplo de comunicación AXI-Stream [8].

# 3.5 AD9467-FMC-250EBZ

AD9467-FMC-250EBZ es una tarjeta de evaluación basada en el componente AD9467 y desarrollada por ANALOG DEVICES. Dicha tarjeta está diseñada para funcionar como un periférico externo de la Zedboard, estableciendo conexión con ella por medio del puerto FMC del que dispone. Además, incorpora un distribuidor de reloj, el AD9517, que permite generar un reloj de frecuencia arbitraria sin necesidad de una fuente externa.

# 3.5.1 AD9467

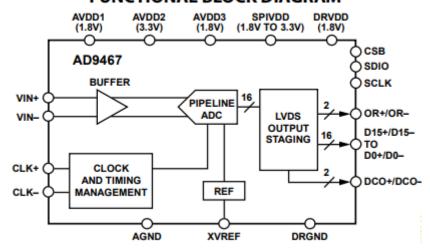

El AD9467 es un conversor analógico digital (ADC) de 16 bits. Está optimizado para un alto rendimiento sobre anchos de banda amplios. Funciona con una tasa de conversión de 250 MSPS y está diseñado para receptores inalámbricos, instrumentación y equipos de prueba que requieren un alto rango dinámico.

# 3.5.1.1 Teoría de operación

La arquitectura del AD9467 está conformada por un ADC segmentado con buffer de entrada que consta de una primera etapa de 3 bits, una segunda de 4 bits, seguida de cuatro etapas de 3 bits y una etapa flash final de 3 bits. Un flash ADC es un tipo de conversor que hace uso de una arquitectura dividida en varios niveles, cada uno de los cuales compara la señal de entrada con unos voltajes de referencia. Para más información se puede consultar la referencia [13], en la que el fabricante de la placa explica esta cuestión más a fondo.

Cada una de las etapas mencionadas proporciona un grado de superposición suficiente como para corregir los posibles errores de flash que puedan suceder en etapas precedentes. Además, el buffer está optimizado para alta linealidad, bajo ruido y baja potencia. Las salidas cuantificadas de cada etapa se combinan en una final, resultando una palabra de 16 bits en la lógica de corrección digital. La Figura 15 muestra un diagrama de bloques con la arquitectura del componente en cuestión.

# **FUNCTIONAL BLOCK DIAGRAM**

Figura 15: Arquitectura del AD9467 [16].

Los muestreos se llevan a cabo en el flanco ascendente del reloj. Cada etapa del buffer de entrada, excluyendo la última, consta de un flash ADC de baja resolución conectado a un DAC de capacidades conmutadas. La última etapa consiste simplemente en un flash ADC. El bloque de preparación de salida alinea los datos, corrige errores y pasa los datos a los buffers de salida.

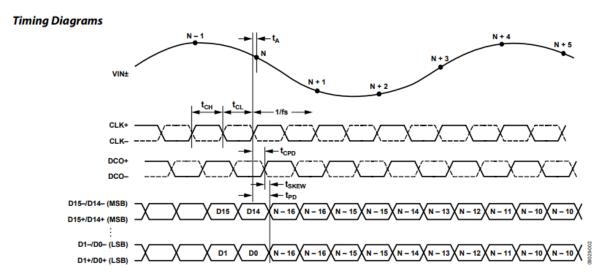

El componente hace uso del modo source-synchronous para la transmisión de las señales de datos por el puerto de salida, que consiste en acompañar dichas señales con un reloj de salida sincronizado (Data Clock Output). En los flancos de subida del reloj se transmitirá un dato y en los flancos de bajada el otro. La Figura 16 esclarece la teoría de operación ilustrando un diagrama temporal de las señales del componente.

Figura 16: Diagrama temporal de las señales del AD9467 [16].

# 3.5.1.2 Interfaz de puerto serie (SPI)

La interfaz de puerto serie del AD9467 brinda al usuario la posibilidad de llevar a cabo acciones de configuración sobre el dispositivo, escribiendo y leyendo sobre las direcciones de memoria de un mapa de registros. Dicha memoria se organiza en bytes, que a su vez se pueden dividir en diferentes campos. Se pueden encontrar más especificaciones sobre la funcionalidad de cada byte de los registros en la nota de aplicación AN-877 [19] que proporciona ANALOG DEVICES.

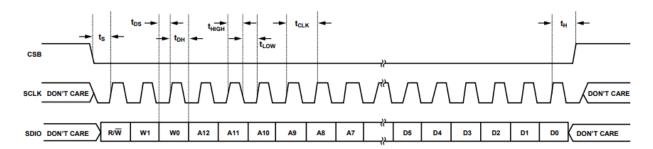

Hay tres pines que definen el funcionamiento de la interfaz SPI: SCLK, SDIO y CSB. El pin SCLK es el reloj de sincronismo de la interfaz y se utiliza para sincronizar la lectura y escribir los datos enviados al ADC. El pin SDIO es un pin bidireccional que permite enviar y leer datos desde los registros internos del mapa de memoria del ADC. El pin CSB es activo a nivel bajo y activa o desactiva los ciclos de lectura y escritura.

Figura 17: Comunicación SPI [16].

En la Figura 17 se puede observar un ejemplo de transmisión con el protocolo SPI. La estructura del mensaje a enviar en el puerto SDIO consta de un primer bit que determina si el proceso a realizar es de escritura o lectura, seguido de dos bits con los que se especifica el número de bytes a leer/escribir (uno, dos, tres o indefinidos), a continuación se encuentran trece bits con los que se debe indicar la dirección de memoria del banco de registros a la que se quiere acceder, y por último, los datos con un tamaño variable de uno, dos o tres bytes dependiendo de la selección del usuario.

## 3.5.2 AD9517

El AD9517 es un generador de reloj con un VCO (oscilador controlado por tensión) integrado de 1,6 GHz, aunque también se puede hacer uso de un VCO externo de hasta 2,4 GHz. Dispone de cuatro salidas LVPECL (en dos pares) y cuatro salidas LVDS (en dos pares). Cada salida LVDS se puede reconfigurar como CMOS. Las salidas LVPECL funcionan a 1,6 GHz, las LVDS a 800 MHz y las CMOS a 250 MHz. La Figura 18 muestra un diagrama de bloques con la arquitectura del componente en cuestión.

### FUNCTIONAL BLOCK DIAGRAM TCHOVER REFIN ᠴ SWI DIVIDER AND MUXs $\text{DIV}/\Phi$ LVPECL ООUТ1 ООUТ2 LVPEC 🗅 оитз OUT4 LVDS/CMOS DIV/m DIV/Φ **∑** о∪т₅ OUT6 DIV/Φ LVDS/CMO: 5 out7 SERIAL CONTROL PORT AD9517-4 AND DIGITAL LOGIC

Figura 18: Diagrama de bloques del AD9517 [17].

El modo de funcionamiento del componente es simple, se puede seleccionar como frecuencia base el VCO interno o uno externo. Una vez seleccionado, se indica la división que se desea realizar a la frecuencia base y la salida que se va a emplear. El rango de división para las salidas LVPECL es de 1 a 32. Las salidas LVDS/CMOS permiten un rango de divisiones hasta un máximo de 1024. Además, el integrado incluye una interfaz de puerto serie para realizar configuraciones internas, idéntico al expuesto para el AD9467.

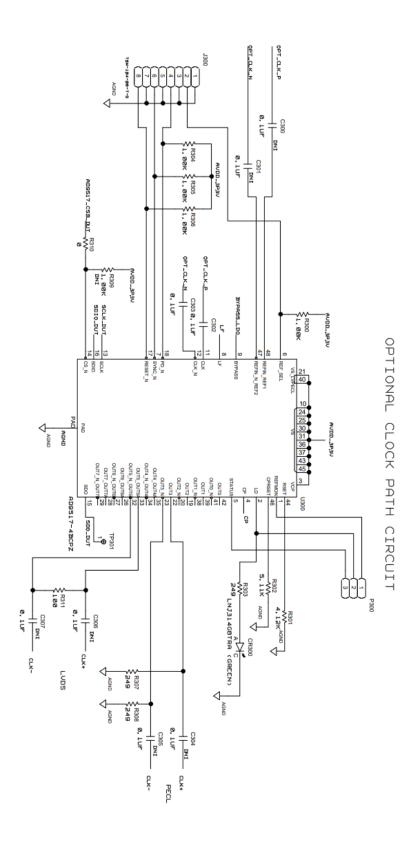

La tarjeta FMC incorpora un AD9517 integrado. La entrada de reloj externa está conectada a un oscilador de 250 MHz, y la salida a utilizar es la tres, que es de tipo LVPECL. El conexionado se puede observar en la Figura 19.

Figura 19: Conexionado del AD9517 en la tarjeta AD9467-FMC-250EBZ [18].

# 3.6 Desarrollo del diseño hardware con Xilinx Vivado

Para llevar a cabo el diseño hardware se ha utilizado la herramienta de diseño Vivado, en concreto la versión 2017.4. Esta dispone de una interfaz gráfica y asistentes que facilitan mucho su uso, pero puede emplearse vía comandos tol desde la terminal de la aplicación o desde el sistema operativo.

Si se hace uso de la interfaz gráfica, a medida que se va avanzando en el desarrollo del proyecto se van mostrando en la consola los comandos tel necesarios para realizar cada acción. Es interesante ir guardando dichos comandos en un documento de extensión .tel para agilizar el proceso de creación del proyecto en otro terminal y poder guardar el proyecto ocupando muy poca memoria.

Tras crear un nuevo proyecto y especificar la tarjeta de desarrollo a utilizar, es necesario realizar la arquitectura hardware del sistema. Dicha arquitectura se puede desarrollar creando un diagrama de bloques con el asistente que proporciona Vivado. El diagrama está conformado por IP (Intellectual Property) Cores, que son bloques de circuitos digitales prediseñados que se pueden usar para agregar una funcionalidad específica a un diseño de FPGA.

Vivado incluye una amplia librería de IP Cores que abordan muchas de las funcionalidades básicas de la placa. La piedra angular de todo diagrama de bloques es el IP Core referente al sistema de procesamiento de la tarjeta a usar.

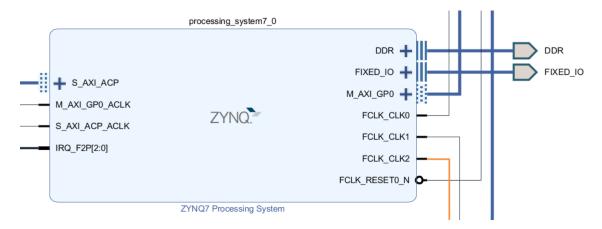

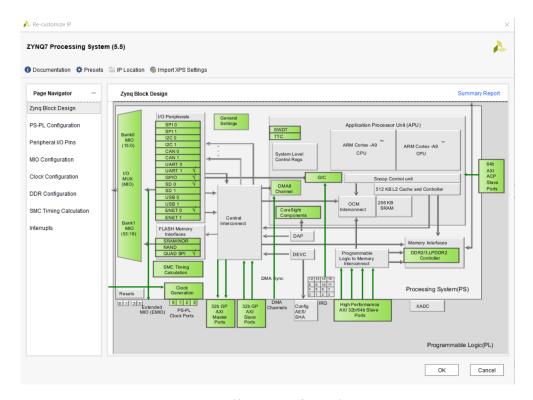

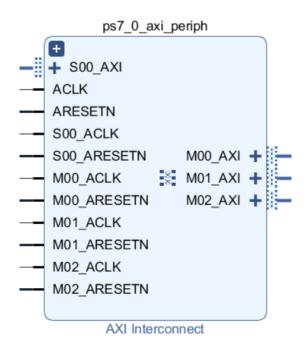

En nuestro caso, al tratarse de la Zedboard, el IP Core es el "ZYNQ7 Processing System" y permite establecer la comunicación entre el PS y la PL de la placa por medio de interconexiones AXI, las cuales son claves para el desarrollo óptimo del sistema. Además, el bloque presenta un gran número de parámetros configurables como relojes del sistema, interrupciones, timers y buses AXI, entre otros.

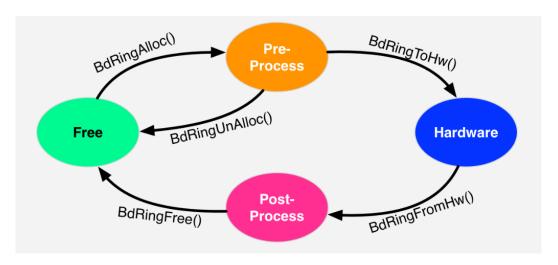

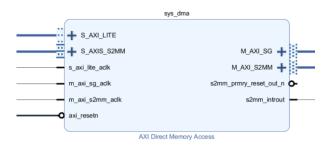

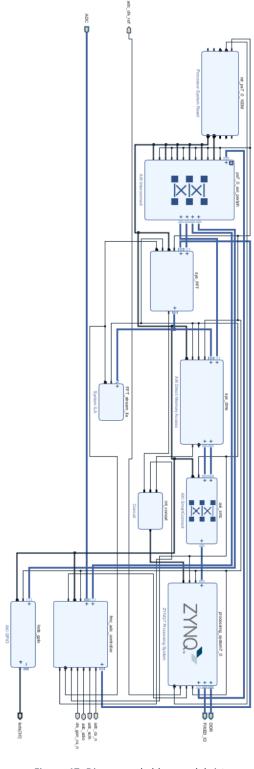

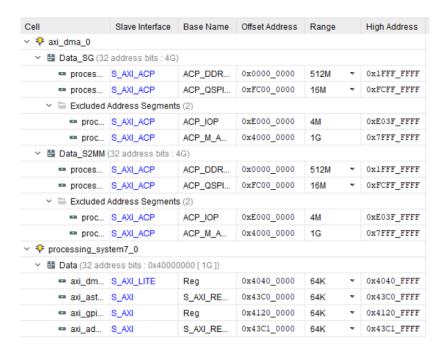

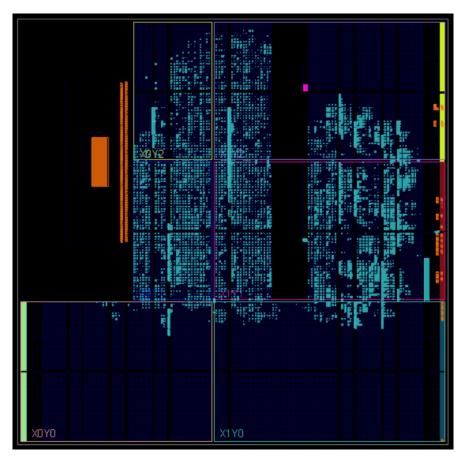

Los bloques a usar en un diagrama no están limitados a los que Xilinx ofrece en sus librerías por defecto, si no que la propia herramienta brinda la posibilidad de crear IP Cores a medida con la opción "Create and package IP". En este punto, surge un pequeño problema, ya que, para garantizar el correcto funcionamiento del IP a medida, una vez implementado en la arquitectura, es preciso realizar pruebas de simulación. Si hacemos uso del bloque "ZYNQ7 Processing System" estas simulaciones se deben realizar con el hardware volcado en placa, lo cual no es nada práctico, ya que ante cualquier fallo será preciso sintetizar e implementar el hardware de nuevo para modificar el código de nuestro IP. Por ello, la solución más razonable es hacer uso de un modelo BFM (Bus Functional Model) del sistema de procesamiento. Esto es una interfaz software que se comporta de la misma manera que el PS de la placa, permitiendo la simulación del software sin necesidad de volcar el hardware en placa.