#### ACTA DE EVALUACIÓN DE LA TESIS DOCTORAL

(FOR EVALUATION OF THE ACT DOCTORAL THESIS)

Año académico (academic year): 2016/17

DOCTORANDO (candidate PHD): SANZ ALONSO, INÉS D.N.I. / PASAPORTE(Id.Passport): \*\*\*\*328W PROGRAMA DE DOCTORADO (Academic Committee of the Programme): D332 DOCTORADO EN ELECTRÓNICA:SISTEMAS ELECTRÓNICOS AVANZADOS.SISTEMAS INTELIGEN DEPARTAMENTO DE (Department): ELECTRÓNICA TITULACIÓN DE DOCTOR EN (Phd title): DOCTOR/A POR LA UNIVERSIDAD DE ALCALÁ

En el día de hoy 16/06/17, reunido el tribunal de evaluación, constituido por los miembros que suscriben el presente Acta, el aspirante defendió su Tesis Doctoral con Mención Internacional (In today assessment met the court, consisting of the members who signed this Act, the candidate defended his doctoral thesis with mention as International Doctorate), elaborada bajo la dirección de (prepared under the direction of) EMILIO JOSÉ BUENO PEÑA // FRANCISCO JAVIER RODRÍGUEZ SÁNCHEZ.

Sobre el siguiente tema (Title of the doctoral thesis): COMPARATIVE ANALYSIS OF MULTILEVEL CONVERTERS FOR MEDIUM-VOLTAGE APPLICATIONS

Finalizada la defensa y discusión de la tesis, el tribunal acordó otorgar la CALIFICACIÓN GLOBAL<sup>2</sup> de (no apto, aprobado, notable y sobresaliente) (After the defense and defense of the thesis, the court agreed to grant the GLOBAL RATING (fail, pass, good and excellent):  $\_$  <u>SOBALESALESALESALESALESALES</u>

Fdo. (Signed): Die Jorthan USN 441/4 Fdo. (Signed): FRANSISCO HUSETA Fdo. (Signed): FRANCISCO DAVIOR FREDDO FRENDEDEZ

FIRMA DEL ALUMNO (candidate's signature),

INES SAN Fdo. (Signed): ....

Con fecha 29 de <u>a conico</u> de <u>2017</u> la Comisión Delegada de la Comisión de Estudios Oficiales de Posgrado, a la vista de los votos emitidos de manera anónima por el tribunal que ha juzgado la tesis, resuelve:

Conceder la Mención de "Cum Laude" No conceder la Mención de "Cum Laude"

La Secretaria de la Comisión Delegada

Droclo

<sup>2</sup> La calificación podrá ser "no apto" "aprobado" "notable" y "sobresaliente". El tribunal podrá otorgar la mención de "cum laude" si la calificación global es de sobresaliente y se emite en tal sentido el voto secreto positivo por unanimidad. (*The grade may be "fail" "pass" "good"* or "excellent". The panel may confer the distinction of "cum laude" if the overall grade is "Excellent" and has been awarded unanimously as such after secret voting.).

INCIDENCIAS / OBSERVACIONES: (Incidents / Comments)

C. S. Kalinis, M. S. S. S. S. S. D. Stell, "groups, mateginger for a Continuously groupbut an ability of "superiods of "superiod and mathematication of mathematication formed and set mathematication of a "Complete L. J. Comput. A publication of a "Complete L. J. Complete L. J. Complet

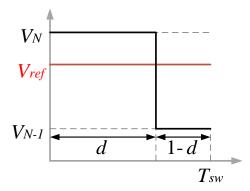

s phage 11 distant of a period d

En aplicación del art. 14.7 del RD. 99/2011 y el art. 14 del Reglamento de Elaboración, Autorización y Defensa de la Tesis Doctoral, la Comisión Delegada de la Comisión de Estudios Oficiales de Posgrado y Doctorado, en sesión pública de fecha 29 de junio, procedió al escrutinio de los votos emitidos por los miembros del tribunal de la tesis defendida por SANZ ALONSO, INÉS, el día 16 de junio de 2017, titulada COMPARATIVE ANALYSIS OF MULTILEVEL CONVERTERS FOR MEDIUM-VOLTAGE APPLICATIONS, para determinar si a la misma se le concede la mención "cum laude", arrojando como resultado, 3 votos en contra.

Por lo tanto, la Comisión de Estudios Oficiales de Posgrado resuelve no otorgar la Mención de "cum laude" a dicha Tesis.

Alcalá de Henares, 11 de julio de 2017 EL PRESIDENTE DE LA COMISIÓN DE ESTUDIOS OFICIALES DE POSGRADO Y DOCTORADO

Juan Ramón Velasco Pérez

Copia por e-mail a: Doctorando: SANZ ALONSO, INÉS Secretario del Tribunal: FRANCISCO HUERTA SÁNCHEZ. Directores de Tesis: EMILIO JOSÉ BUENO PEÑA//FRANCISCO JAVIER RODRÍGUEZ SÁNCHEZ

Posgrado

| DILIGENCIA DE DEPÓSITO DE TESIS.                                                                                                                                                                                                                                                                                 |                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Comprobado que el expediente académico de D./D <sup>a</sup><br>reúne los requisitos exigidos para la presentación de la Tesis, de acuerdo a la r<br>presentado la misma en formato: soporte electrónico impreso en<br>misma, en el Servicio de Estudios Oficiales de Posgrado, con el n <sup>o</sup> de páginas: | normativa vigente, y habiendo<br>papel, para el depósito de la |

| fecha de hoy a registrar el depósito de la tesis.<br>Alcalá de Henares a de                                                                                                                                                                                                                                      | de 20                                                          |

| A D D C A D D C A D D C A D D C A D D C A D D C A D D C A D D C A D D C A D D C A D D C A D D C A D D D C A D D D C A D D D D                                                                                                                                                                                    | Fdo. El Funcionario                                            |

### Universidad de Alcalá

Departamento de Electrónica

Doctorado en Electrónica: Sistemas Electrónicos Avanzados. Sistemas Inteligentes.

PhD Thesis

# COMPARATIVE ANALYSIS OF MULTILEVEL CONVERTERS FOR MEDIUM-VOLTAGE APPLICATIONS

Inés Sanz Alonso

Supervisors: Dr. Emilio José Bueno Peña

Dr. Francisco Javier Rodríguez Sánchez

DEPARTAMENTO DE ELECTRÓNICA

Edificio Politécnico Campus Universitario s/n 28805 Alcalá de Henares (Madrid) Teléfono: 91 885 65 40 Fax: 91 885 65 91 eldep@depeca.uah.es

Dr. Emilio José Bueno Peña, Profesor Titular de la Universidad de Alcalá, y Dr. Francisco Javier Rodríguez Sánchez, Profesor Catedrático de la Universidad Alcalá,

INFORMAN: Que la Tesis Doctoral titulada "Comparative Analysis of Multilevel Converters for Medium Voltage Applications" presentada por D<sup>a</sup>. Inés Sanz Alonso, y realizada bajo la dirección de los doctores D. Emilio José Bueno Peña y D. Francisco Javier Rodríguez Sánchez, dentro del campo de la aplicación de los convertidores multinivel para aplicaciones de media tensión, reúne los méritos de calidad y originalidad para optar al Grado de Doctor.

Alcalá de Henares, 30 de Marzo de 2017

Fdo. Émilio José Bueno Peña

ENTO \* Fdo. Francisco Javier Rodríguez Sánchez

UNIVERSIDAD DE ALCALÁ, PATRIMONIO DE LA HUMANIDAD

DEPARTAMENTO DE ELECTRÓNICA

Edificio Politécnico Campus Universitario s/n 28805 Alcalá de Henares (Madrid) Teléfono: 91 885 65 40 Fax: 91 885 65 91 eldep@depeca.uah.es

Dra. Sira Elena Palazuelos Cagigas, Directora del Departamento de Electrónica de la Universidad de Alcalá,

**INFORMA:**

Que la Tesis Doctoral titulada "Comparative Analysis of Multilevel Converters for Medium Voltage Applications" presentada por Da. Inés Sanz Alonso, y dirigida por los doctores D. Emilio José Bueno Peña y D. Francisco Javier Rodríguez Sánchez, cumple con todos los requisitos científicos y metodológicos, para ser defendida ante un Tribunal, según lo indicado por la Comisión Académica del Programa de Doctorado.

Alcalá de Henares, 30 de Marzo de 2017

Fdo. Sira Elena Palazuelos Cagigas

#### ABSTRACT

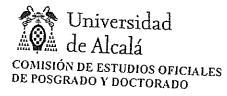

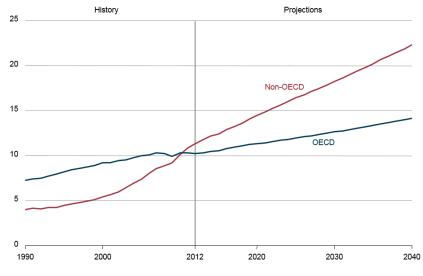

The electric energy demand has been steadily growing during the last century, and all forecasts indicate that it will keep growing in the following years. Within this frame, and due to all the problems that this demand increase generate in the environment, it is necessary improving the current techniques of electric energy conversion and transmission in order to increase the whole system efficiency. On the other hand, it is also necessary increasing the renewable energy resources exploitation through more efficient generation systems.

According to these lines, the power electronics systems that have been installed in the last decades allowed to obtain better efficiency from the renewable natural resources like the wind or the solar power. These systems have also notably improved the quality of the power supplied, reducing the losses through what are known as power quality applications.

Power converters are currently essential in any power electronics system. Within them, the multilevel converters specially suppose a breakthrough compared with the classical two-level converters, as they allow obtaining voltage and current signals with lower harmonic content, what means fewer losses in high-power medium-voltage applications.

In this Thesis a comparative study of some multilevel converter topologies normally used in high-power medium-voltage applications is done. The objective is analyzing in detail each topology and comparing it with the rest following different criteria, with the aim to know the advantages and drawbacks of each one and to realize which one is more suitable for each application.

## RESUMEN

El consumo de energía eléctrica no ha parado de crecer en el último siglo, y todas las previsiones apuntan a que lo va a seguir haciendo en los próximos años. Dentro de este marco, y debido a los problemas que este incremento en el consumo genera en el medio ambiente, se hace necesario mejorar las técnicas actuales de conversión y transmisión de energía eléctrica para incrementar la eficiencia del sistema completo. Por otro lado, se hace necesario incrementar el aprovechamiento de los recursos energéticos renovables mediante sistemas de generación más eficientes.

Siguiendo esas líneas, los sistemas de electrónica de potencia que se han ido instalando en las últimas décadas han permitido obtener un mejor aprovechamiento de los recursos naturales como el viento o la luz solar, y además han mejorado notablemente la calidad de la energía suministrada, reduciendo las pérdidas a través de lo que se conoce como aplicaciones de "*power quality*".

Los convertidores de potencia son actualmente indispensables en cualquier sistema de electrónica de potencia. Dentro de ellos, especialmente los convertidores multinivel suponen un gran avance respecto a los convertidores clásicos de dos niveles, ya que permiten obtener señales con menos contenido armónico, lo que se traduce en menos pérdidas en los sistemas de media tensión y alta potencia.

En esta Tesis se hace un estudio comparativo de varias topologías de convertidores multinivel que suelen utilizarse en aplicaciones de media tensión y alta potencia. El objetivo es analizar pormenorizadamente cada topología y compararla con las demás en base a diferentes criterios, con el propósito de conocer los puntos fuertes y débiles de cada una y discernir cuál es más adecuada para cada aplicación.

## AGRADECIMIENTOS

Esta Tesis es fruto de los trabajos realizados por su autora dentro del grupo de investigación GEISER durante los últimos cuatro años y medio. Durante este periodo han sido muchas personas las que han influido en la consecución de dicho trabajo. Sirvan estas palabras como reconocimiento para todas ellas aunque no sean mencionadas expresamente.

En primer lugar me gustaría dar las gracias a los supervisores de mi trabajo, los doctores Emilio Bueno y Fco. Javier Sánchez, por tomarse la molestia de revisar todo este trabajo, y poner a mi disposición los recursos del grupo de investigación. Agradezco especialmente tu labor, Emilio, por todo lo que me has enseñado, la paciencia que has tenido conmigo, y la confianza que depositaste en mí el día que me fichaste (de verdad, doy gracias por haberme encontrado de casualidad aquel día contigo).

También quiero agradecer a todos los compañeros con los que he coincidido en el grupo de investigación, por los conocimientos compartidos, o simplemente por los buenos ratos que hemos pasado trabajando (a la mente me llegan recuerdos de charlas con los doctores Mario Rizo o Rafa Peña...). Me gustaría agradecer especialmente a Miguel Moranchel todo lo que me ha enseñado, el haber tenido una actitud tan positiva en el trabajo, y el haberme prestado su ayuda en innumerables ocasiones; sin duda, ha sido un placer tenerte como compañero durante estos años.

Agradezco también la compañía y los buenos ratos pasados con el resto de compañeros de otros grupos de investigación, especialmente con Laura, Susel, y Marco, y con los compis de café: Luis, Diego, Germán y CJ.

Por otro lado quiero agradecer el apoyo que me ha brindado mi familia: agradezco a mi padre que luchara por vivir y poder estar hoy a mi lado, y que me animara en todo momento a avanzar más y más; doy gracias a mi madre por haber sido mi mayor fan y haberme hecho creer en mí misma, aunque perdiera la batalla su recuerdo y sus enseñanzas seguirán vivas para siempre; doy gracias a mis hermanos por ser como son, por estar a mi lado, por traer a mi vida a mis sobrinas que han supuesto una alegría tan grande... Aunque todavía sean pequeñas, espero que algún día entiendan lo que significan para mí y lo que han ayudado en este trabajo. Haré mención especial a mi hermana Bea, la primera doctora Sanz de nuestra familia, por todo su apoyo y por haberme puesto el listón tan alto y animarme siempre a superarlo. También quiero agradecer a Javi el haber estado a mi lado desde hace tanto, y su disposición a ayudarme en cualquier situación. También agradezco al resto de mi familia, a mis tíos y primos, todo su cariño y apoyo.

Por último quiero dedicar unas palabras de agradecimiento a todos los amigos que han estado pendientes de la evolución de este trabajo, animándome en los malos ratos, y procurándome un poco de necesaria distracción de cuando en cuando. A todos vosotros, gracias.

# GLOSSARY

| AC    | Alternating current                    |

|-------|----------------------------------------|

| ANPC  | Active neutral point-clamped           |

| APOD  | Alternative phase opposite disposition |

| CHB   | Cascaded H-bridge                      |

| DC    | Direct Current                         |

| DNPC  | Diode neutral point-clamped            |

| DPF   | Displacement power factor              |

| DSP   | Digital signals processor              |

| EMF   | Electromotive force                    |

| FACTS | Flexible AC transmission system        |

| FOC   | Field oriented control                 |

| FPGA  | Field programmable gate array          |

| GTO   | Gate turn-off (thyristor)              |

| HV    | High voltage                           |

| HVDC  | High voltage direct current            |

| IGBT  | Insulated gate bipolar transistor      |

| IGCT  | Integrated gate-commutated thyristor   |

| IM    | Induction machine / induction motor    |

| IPD   | In phase disposition                   |

|       |                                        |

| <b>T T</b> 7 | T 1/                                              |

|--------------|---------------------------------------------------|

| LV           | Low voltage                                       |

| MMC          | Modular multilevel converter                      |

| MOSFET       | Metal-oxide-semiconductor field-effect transistor |

| MV           | Medium voltage                                    |

| NLM          | Nearest-level modulation                          |

| NPC          | Neutral point-clamped                             |

| PCC          | Point of common coupling                          |

| PF           | Power factor                                      |

| PI           | Proportional-integral                             |

| PLL          | Phase locked loop                                 |

| POD          | Phase opposite disposition                        |

| PWM          | Pulse-width modulation                            |

| SCR          | Silicon controlled rectifier                      |

| SHE          | Selective harmonic elimination                    |

| SISO         | Single input, single output                       |

| SM           | Submodule                                         |

| SPWM         | Sinusoidal pulse-width modulation                 |

| STATCOM      | STATtic COMpensator                               |

| SVM          | Space vector modulation                           |

| THD          | Total harmonic distortion                         |

| VSC          | Voltage source converter                          |

| WTHD         | Weighted total harmonic distortion                |

| ZOH          | Zero order hold                                   |

# **SUMMARY OF FIGURES AND TABLES**

#### Summary of figures

| Figure 1.1.            | OECD and non-OECD countries electricity generation from 1990 to 2040 in trillion of                                                                        |     |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| kWh (U                 | JS trillion = $10^{12}$ ) [3]                                                                                                                              | . 5 |

| Figure 1.2.            | World electricity generation forecast by fuel in trillion kWh (US trillion = $10^{12}$ ) [3]                                                               | . 6 |

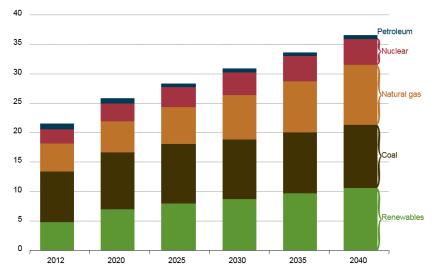

| Figure 1.3.            | Evolution of power switching devices toward the concept of ideal switch [4].                                                                               | . 7 |

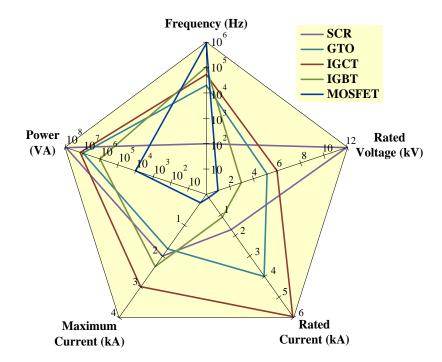

| Figure 1.4.            | Power devices comparison depending on their main parameters [5],[6]                                                                                        | . 8 |

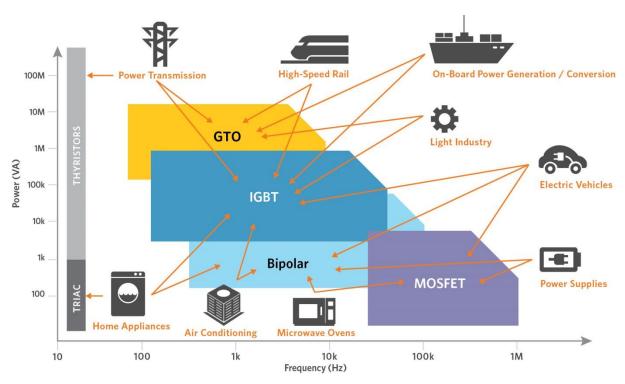

| Figure 1.5.<br>applica | Classification of power devices attending to their power and frequency ranges, and main tion where they are used [7]                                       | . 8 |

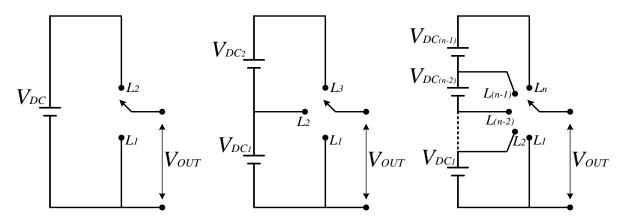

| Figure 1.6. convert    | Illustration of generic two-level converter a), three-level converter b), and n-level ter c)                                                               | .9  |

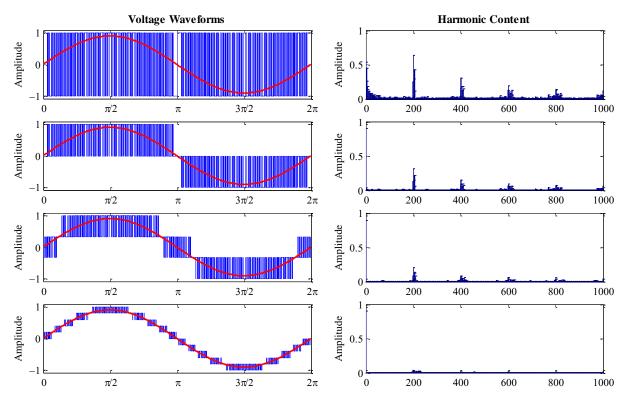

| Figure 1.7.<br>From to | Example of multilevel signals (left) and their corresponding harmonic content (right). pp to bottom: 2-levels waveform, 3-levels, 4-levels, and 11-levels. | 10  |

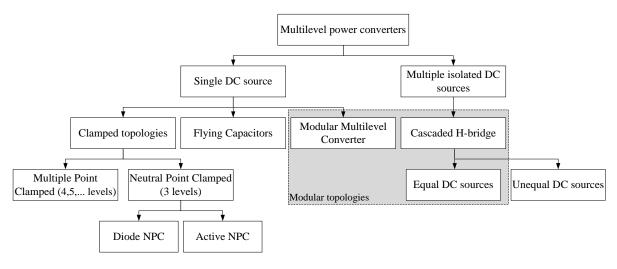

| Figure 2.1.            | Classification of multilevel power converters.                                                                                                             | 18  |

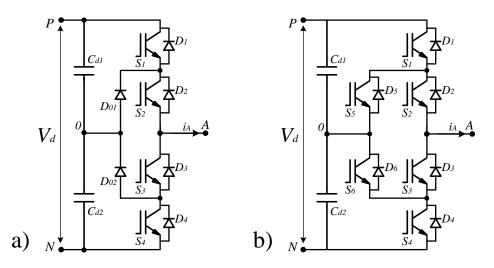

| Figure 2.2.            | Illustration of one phase of a diode neutral point-clamped converter a), and one phase of<br>we neutral point-clamped converter b).                        | 19  |

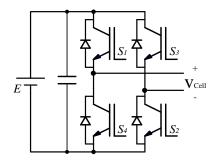

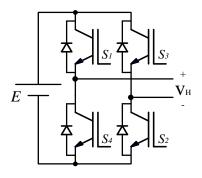

| Figure 2.3.            | Single-phase H-bridge cell.                                                                                                                                |     |

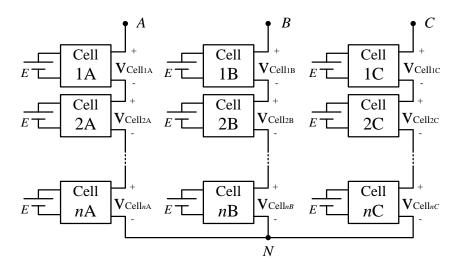

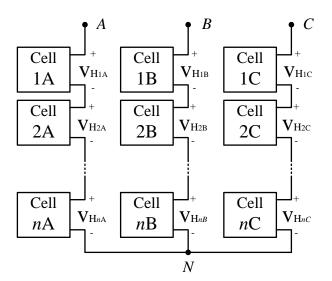

| Figure 2.4.            | Example of a Cascaded H-Bridge converter with n cells per phase                                                                                            |     |

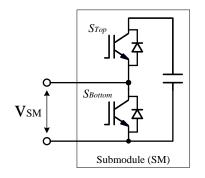

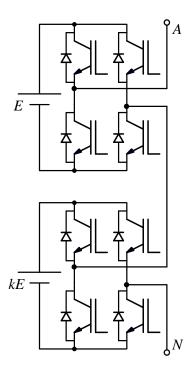

| Figure 2.5.            | 2-Level SubModule (SM)                                                                                                                                     |     |

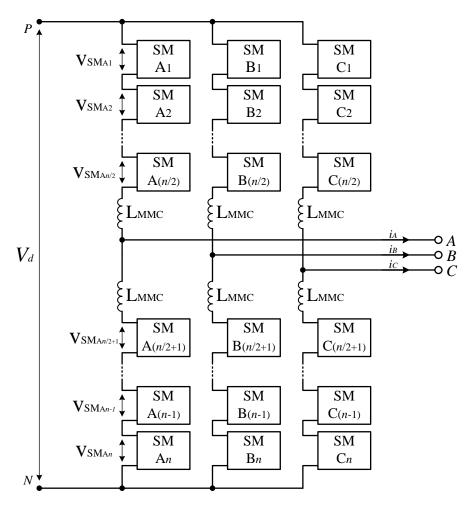

| Figure 2.6.            | Modular multilevel converter with n submodules per phase                                                                                                   | 21  |

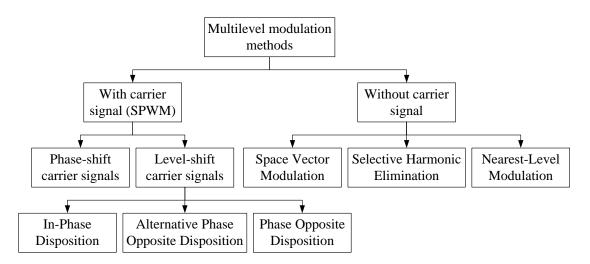

| Figure 2.7.            | Classification of the main modulation methods used in power multilevel converters                                                                          | 22  |

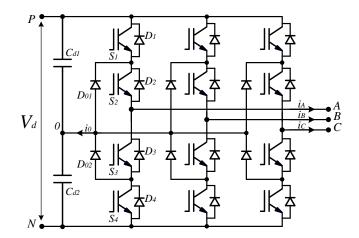

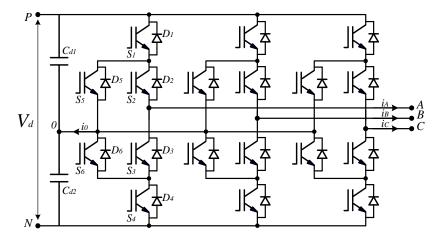

| Figure 3.1.            | Diode Neutral Point Clamped converter with IGBT's.                                                                                                         | 26  |

| Figure 3.2.            | Active Neutral Point Clamped converter with IGBT's.                                                                                                        | 27  |

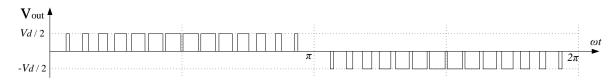

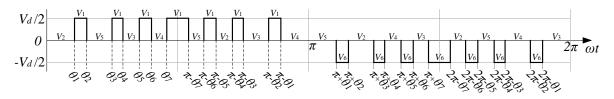

| Figure 3.3.            | Typical phase-to-neutral output voltage in a 3-level converter.                                                                                            | 28  |

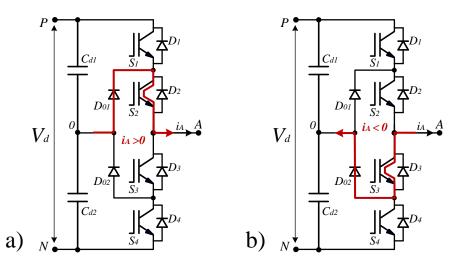

| Figure 3.4.<br>and wh  | Current path in DNPC converter during zero state: when the output current is positive a), en it is negative b)                                             | 29  |

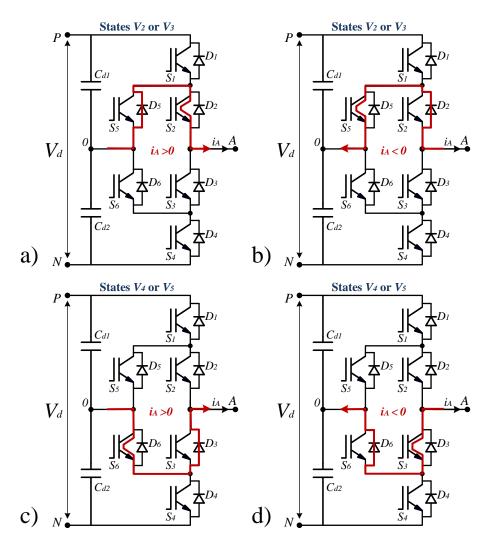

| Figure 3.5. Current path in ANPC converter during zero state: when states $V_2$ or $V_3$ are applied and                                                                                           |            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| the output current is positive a), when those states are selected and the current is negative b),                                                                                                  | •          |

| when $V_4$ or $V_5$ are applied with positive current c), and negative current d)2                                                                                                                 |            |

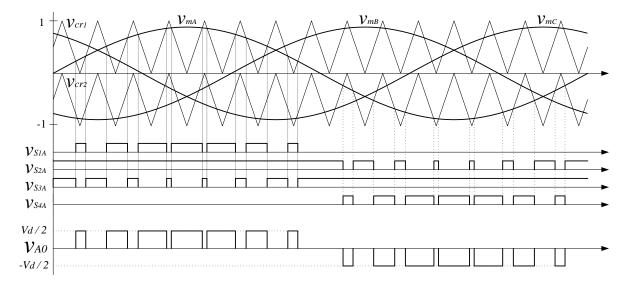

| Figure 3.6. Example of Sinusoidal PWM for a DNPC ( $m_f = 15$ , $m_a = 0.85$ )                                                                                                                     | 51         |

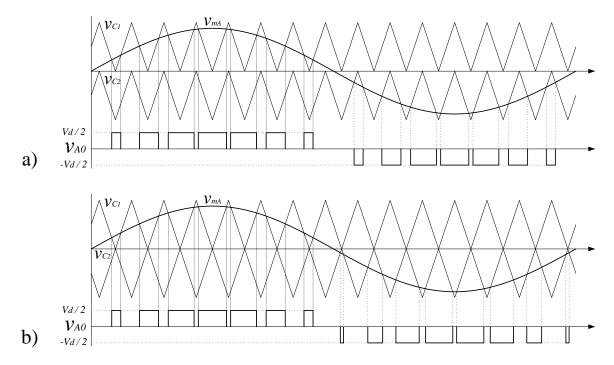

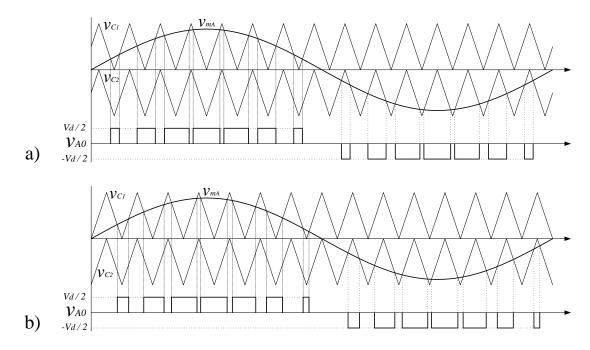

| Figure 3.7. Example of carrier signals "in-phase disposition" - IPD a); and in "phase opposite disposition" - POD b). Both for $m_f = 15$ and $m_a = 0.85$                                         | 32         |

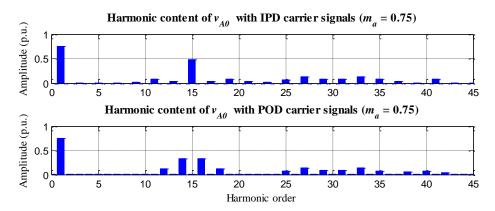

| Figure 3.8. Harmonic content of phase-to-neutral voltage for an amplitude modulation index of 0.75 and $m_f = 15$ when IPD carrier signals are used a); and for POD signals b)                     | 32         |

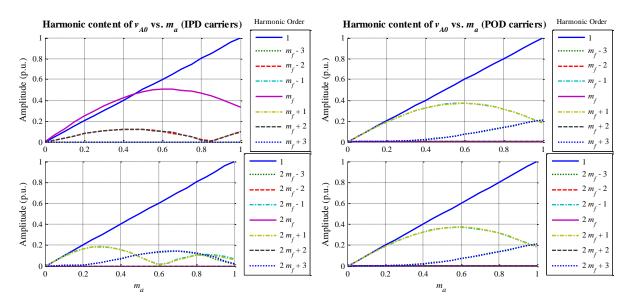

| Figure 3.9. Harmonic content of the phase-to-neutral signal, v <sub>A0</sub> , vs. m <sub>a</sub> when IPD carrier signals are used a); and using POD signals b)                                   | 33         |

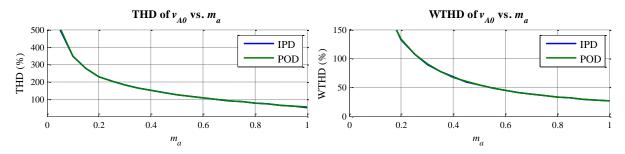

| Figure 3.10. THD and WTHD of the phase-to-neutral voltage, v <sub>A0</sub> , vs. m <sub>a</sub> when IPD carrier signals are used a); and using POD signals b)                                     | 33         |

| Figure 3.11. Example of carrier signals with phase-shift of $\pi/2$ radians a); and without phase-shift b).<br>Both for $m_f = 15$ and $m_a = 0.85$ .                                              | 33         |

| Figure 3.12. Harmonic content of the phase-to-neutral signal, $v_{A0}$ , vs. $m_a$ when carrier signals has $\phi = \pi/2$ a); and when carrier signals has $\phi = 0$ b)                          |            |

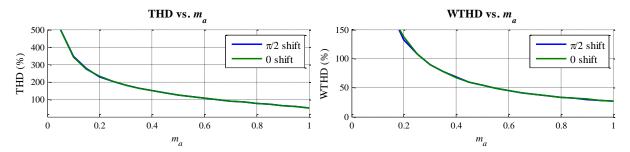

| Figure 3.13. THD and WTHD of the phase-to-neutral voltage, $v_{A0}$ , vs. $m_a$ when carrier signals has                                                                                           |            |

| $\varphi = \pi / 2$ a); and when carrier signals has $\varphi = 0$ b)                                                                                                                              | 34         |

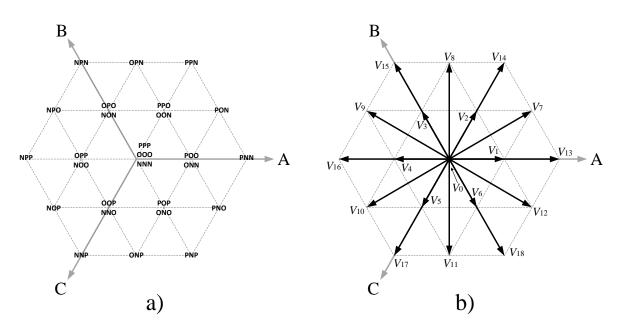

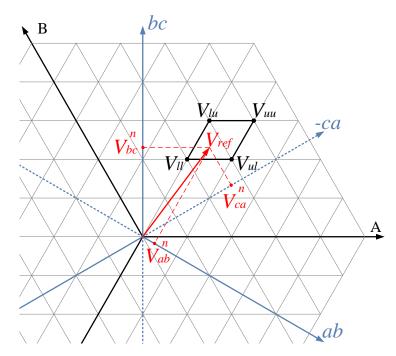

| Figure 3.14. Switching states representation a), and voltage vectors b), in the space vector modulation for a three-level converter                                                                | 36         |

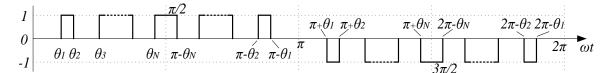

| Figure 3.15. Generic three-levels wave with quarter-wave symmetry                                                                                                                                  | 37         |

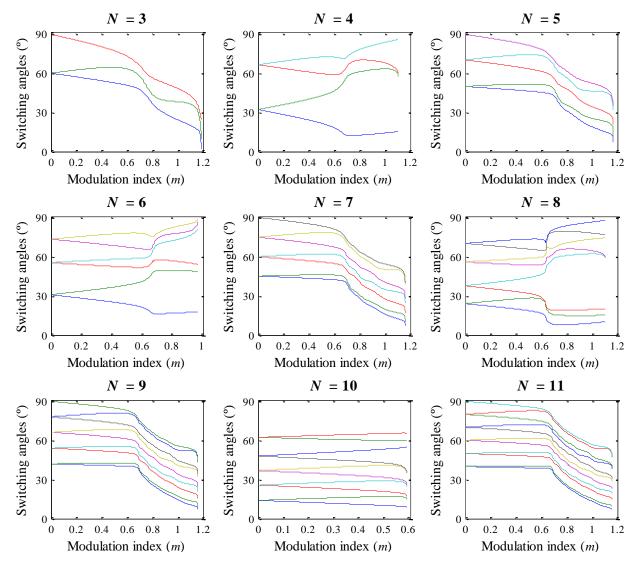

| Figure 3.16. Switching angles vs. amplitude modulation index (m) for a three-phase three-level converter when N comes from 3 to 11                                                                 | 40         |

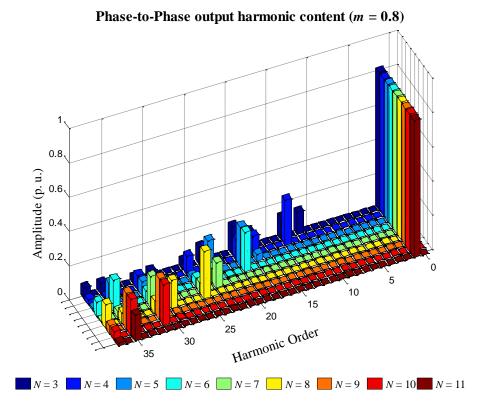

| Figure 3.17. Phase-to-phase output harmonic content when the different sets of angles are used for the same modulation index ( $m = 0.8$ )4                                                        | 41         |

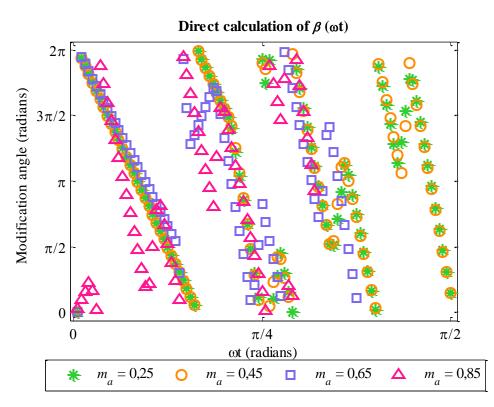

| Figure 3.18. Direct calculation of the modification function, $\beta(t)$ , that is used to approximate the SHE scheme with carrier based modulation                                                | 42         |

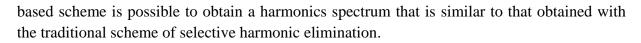

| Figure 3.19. Examples of modified carrier signals calculated with the modification function for different modulation indexes, and phase-to-neutral signal (v <sub>a0</sub> ) obtained in each case | 43         |

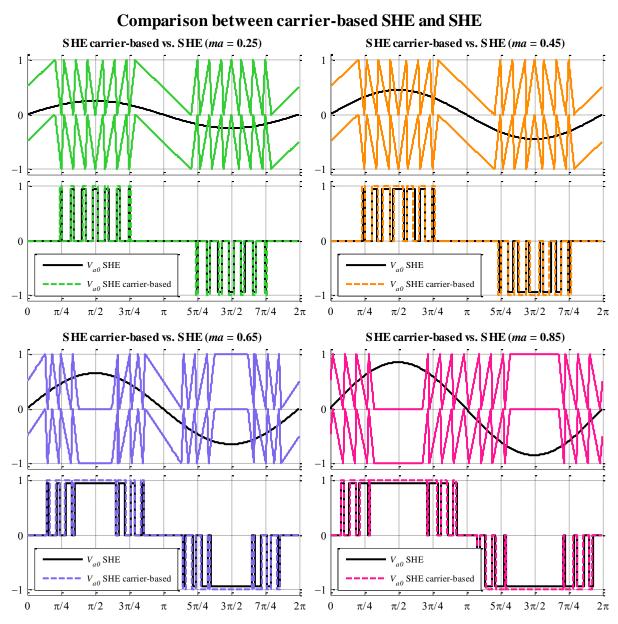

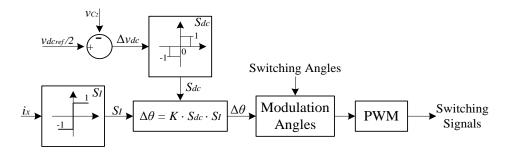

| Figure 3.20. Switching strategy proposed in [50] for SHE modulation ( $N = 7$ )4                                                                                                                   | 14         |

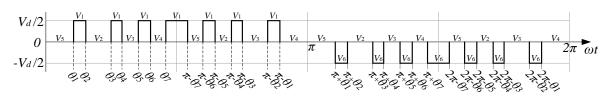

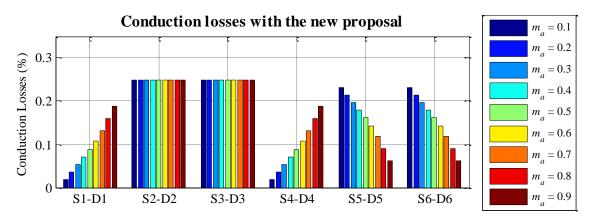

| Figure 3.21. Theoretical conduction losses for the ANPC converter for different modulation indexes                                                                                                 |            |

| using switching pattern from [50]4                                                                                                                                                                 | 14         |

| Figure 3.22. Switching strategy proposed in [42] for SHE modulation (N = 7)4                                                                                                                       | 15         |

| Figure 3.23. Theoretical conduction losses for the ANPC converter for different modulation indexes                                                                                                 |            |

| using switching pattern from [42]4                                                                                                                                                                 | 16         |

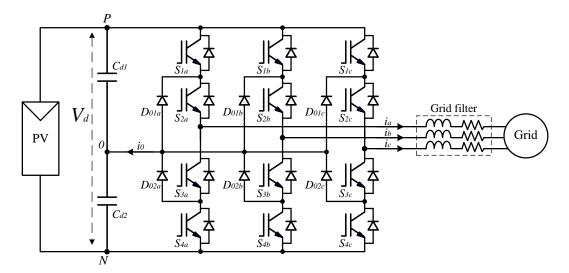

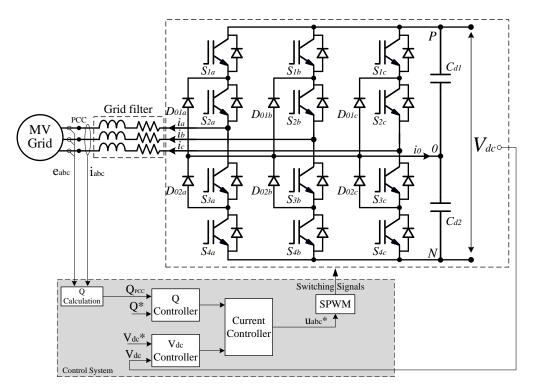

| Figure 3.24. Example of PV panels connection with a distribution grid through a DNPC converter4                                                                                                    | 16         |

| Figure 3.25. Example of wind turbine connection though DNPC converter with back-to-back configuration                                                                                              | <b>1</b> 7 |

| Figure 3.26. Basic scheme of a DNPC-based STATCOM.                                                                                                                                                 | 18         |

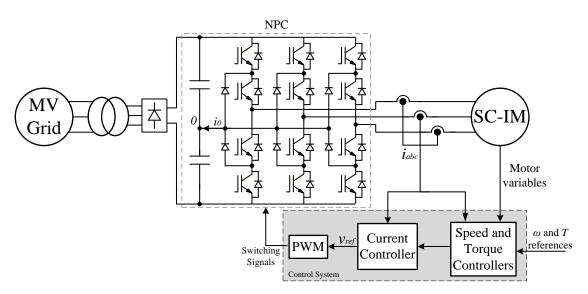

| Figure 3.27. Illustration of a basic MV-drive with a DNPC converter                                                                                                                                | 18         |

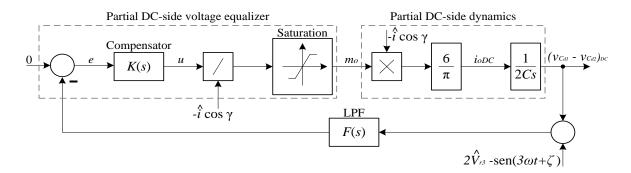

| Figure 3.28. Block diagram of the neutral point voltage balancing method for SHE modulation explained in [50]4                                                                                     | 49         |

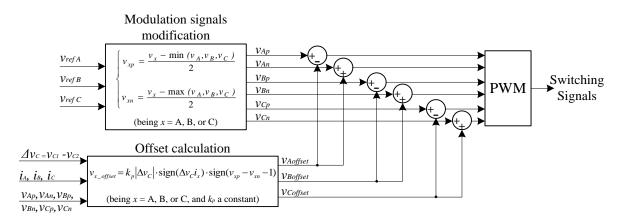

| Figure 3.29. Block diagram of the neutral point voltage balancing method for SPWM modulation explained in [70]4                                                                                    | 49         |

| Figure 3.30. Block diagram of the neutral point voltage balancing method for SPWM modulation explained in [71]4                                                                                    | <b>1</b> 9 |

| Figure 4.1.                | Simplified scheme of a H-bridge cell                                                                                                                                                                                                                                                                                           | . 52 |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 4.2.                | 3-phase CHB converter with 'n' cells per phase                                                                                                                                                                                                                                                                                 | 52   |

| Figure 4.3.                | Branch A of a two-cell CHB converter with unequal DC sources                                                                                                                                                                                                                                                                   | 53   |

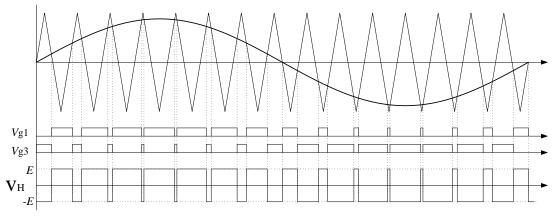

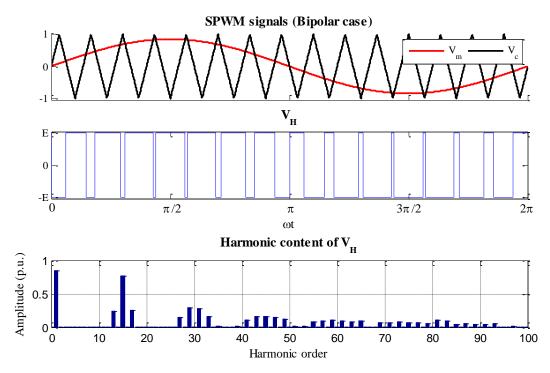

| Figure 4.4.                | Bipolar PWM for a H-bridge cell ( $m_f = 15$ ).                                                                                                                                                                                                                                                                                | 54   |

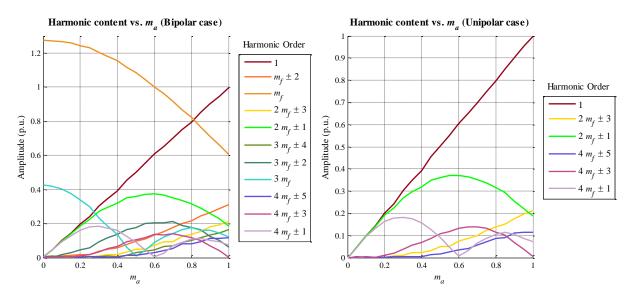

| Figure 4.5.<br>= 750 I     | Harmonic content of the output voltage of a H-bridge using bipolar SPWM ( $f_m = 50$ Hz, $f_c$ Hz, $m_f = 15$ , $m_a = 0.85$ ).                                                                                                                                                                                                |      |

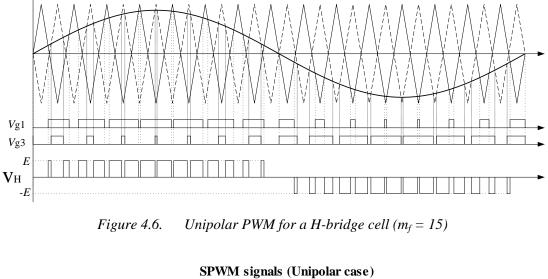

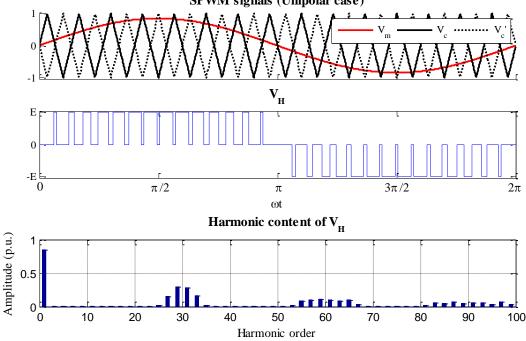

| Figure 4.6.                | Unipolar PWM for a H-bridge cell $(m_f = 15)$                                                                                                                                                                                                                                                                                  | 56   |

| Figure 4.7. $f_c = 75$     | Harmonic content of the output voltage of a H-bridge using unipolar SPWM ( $f_m = 50$ Hz, 0 Hz, $m_f = 15$ , $m_a = 0.85$ ).                                                                                                                                                                                                   |      |

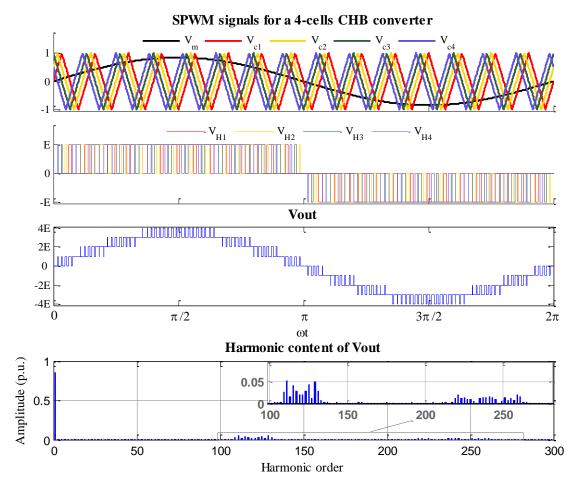

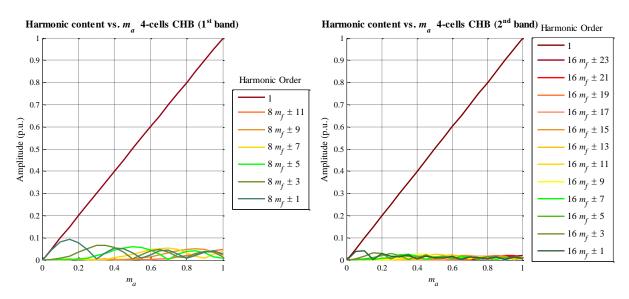

| Figure 4.8.<br>modula      | Harmonic content of the H-bridge output voltage using bipolar (left) and unipolar (right) ation, as a function of the amplitude modulation index, ma.                                                                                                                                                                          |      |

| Figure 4.9.<br>modula      | Total Harmonic Distortion (left) and Weight Total Harmonic Distortion (right) for both ation cases (bipolar and unipolar) as a function of m <sub>a</sub> .                                                                                                                                                                    |      |

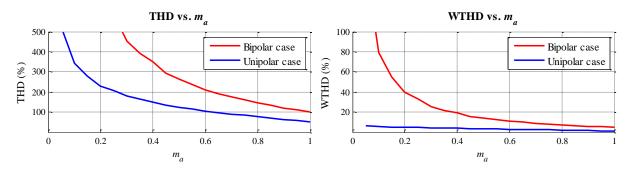

| •                          | Example of PWM for a nine-level (four-cells) CHB converter ( $mf = 15$ , $ma = 0.85$ ). (Note clarity purposes only the master carrier signals have been depicted).                                                                                                                                                            |      |

| Figure 4.11.<br>$m_a$ in a | Amplitude analysis of harmonics in the first band (left) and the second band (right) versus four-cells CHB converter.                                                                                                                                                                                                          |      |

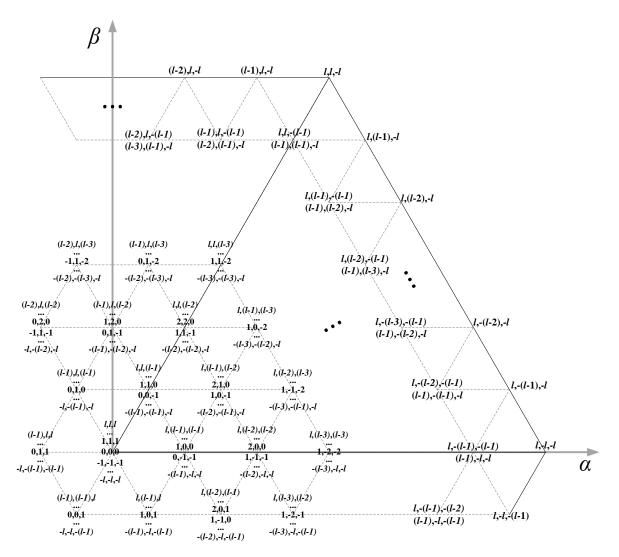

|                            | Detail of the Space Vector hexagon for a generic n-level converter (where l represents the um voltage level of the converter: $l = (n-1)/2$                                                                                                                                                                                    |      |

| Figure 4.13.               | Generic multilevel waveform.                                                                                                                                                                                                                                                                                                   | 62   |

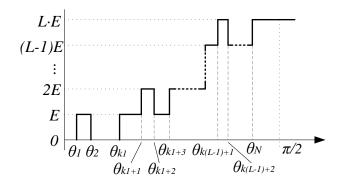

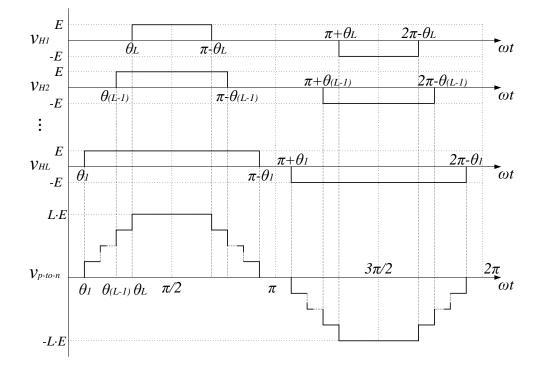

| Figure 4.14.               | Stair-case general waveform for a CHB converter with $L = (n-1)/2$ cells (n-level)                                                                                                                                                                                                                                             | 63   |

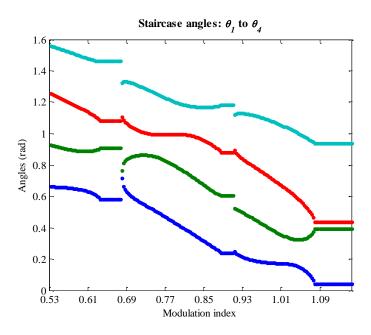

| Figure 4.15.               | Stair-case solution for a 4-cells CHB converter.                                                                                                                                                                                                                                                                               | 64   |

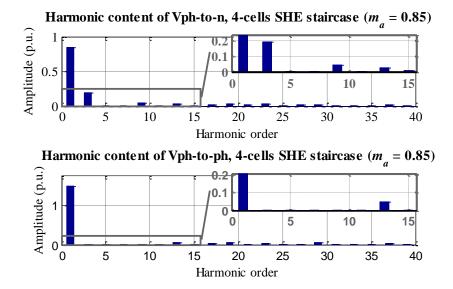

| Figure 4.16.<br>when S     | Harmonic content of the phase-to-neutral (up) and the phase-to-phase (down) voltages Staircase-SHE modulation is applied to a 4-cells CHB converter ( $m_a = 0.85$ )                                                                                                                                                           |      |

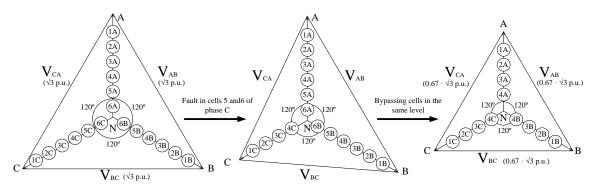

| Figure 4.17.               | Illustration of bypassing the cells of the same level in a six-cells CHB converter                                                                                                                                                                                                                                             | 66   |

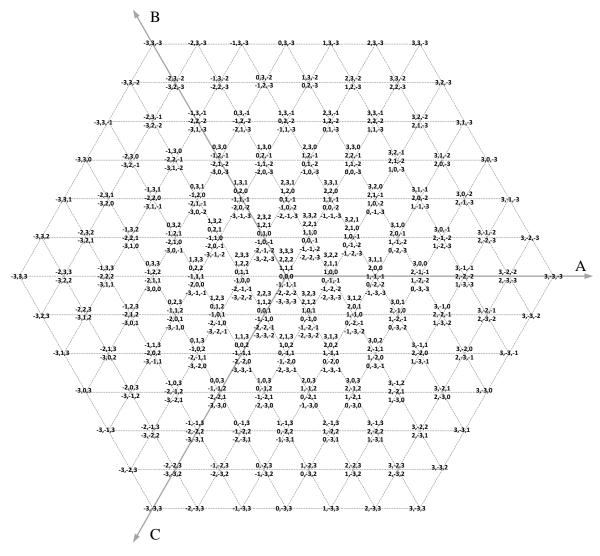

| Figure 4.18.               | Space vectors hexagon for a seven-level CHB converter                                                                                                                                                                                                                                                                          | 67   |

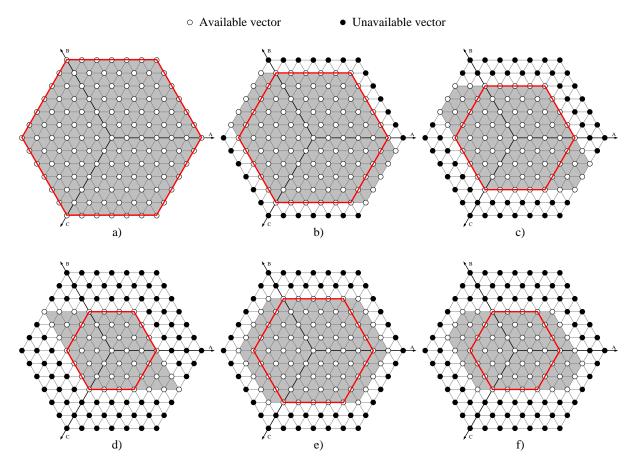

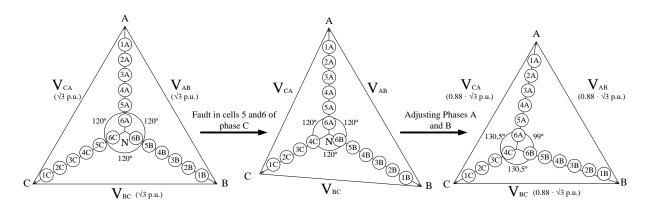

| faulty                     | Representation of the valid switching states for a 7-levels CHB converter in normal on (a), with one faulty cell in phase C (b), with two faulty cells in phase C (c), with three cells in phase C (d), with one faulty cell in phase C and another one in phase B (e), and yo faulty cells in phase C and one in phase B (f). |      |

| Figure 4.20.               | Illustration of neutral shift method in a six-cells CHB converter                                                                                                                                                                                                                                                              | 71   |

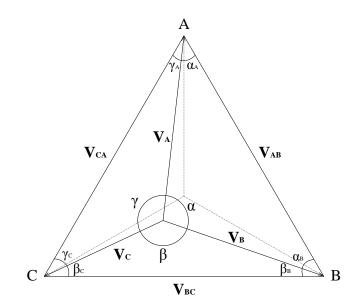

| Figure 4.21.               | Representation of the phase-to-neutral voltages calculation.                                                                                                                                                                                                                                                                   | 72   |

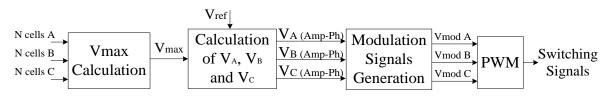

| Figure 4.22.               | Block diagram of the proposed neutral-shift method.                                                                                                                                                                                                                                                                            | 72   |

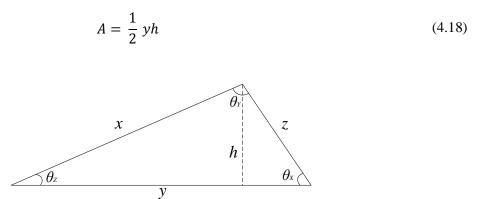

| Figure 4.23.               | Illustration of a generic triangle of sides x, y, z                                                                                                                                                                                                                                                                            | 73   |

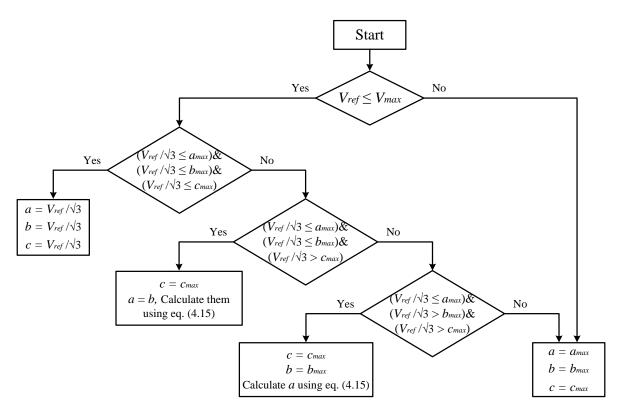

| Figure 4.24.               | Flux-diagram of the neutral-shift calculation process.                                                                                                                                                                                                                                                                         | 75   |

| Figure 4.25.               | Available balanced phase-to-phase voltage with the application of the different balancing                                                                                                                                                                                                                                      |      |

|                            | Is, for CHB converters of 2, 3, 4, 5, 6, 7, and 8 cells per phase. In each graph $N_A$ , $N_B$ , and resent the number of available (non-faulty) cells in the corresponding phase                                                                                                                                              |      |

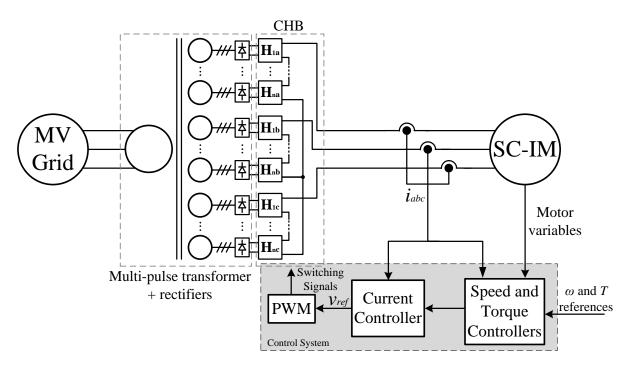

| Figure 4.26.               | Basic scheme of an induction motor drive based on CHB converter.                                                                                                                                                                                                                                                               | 82   |

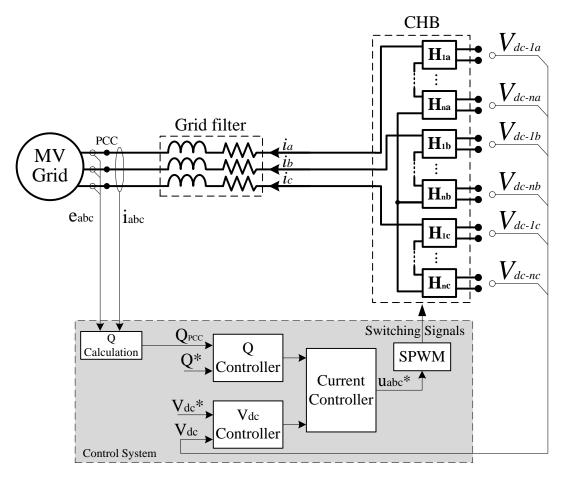

| Figure 4.27.               | Illustration of CHB converter used for a STATCOM system.                                                                                                                                                                                                                                                                       | 83   |

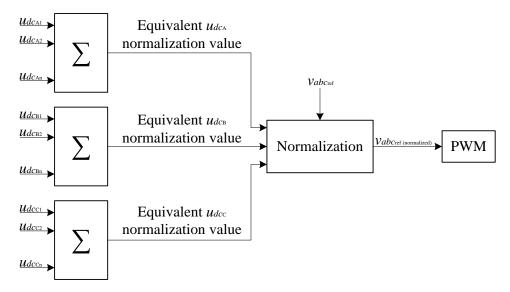

| Figure 4.28.               | Block diagram for the voltage references normalization process in the CHB converter                                                                                                                                                                                                                                            | 84   |

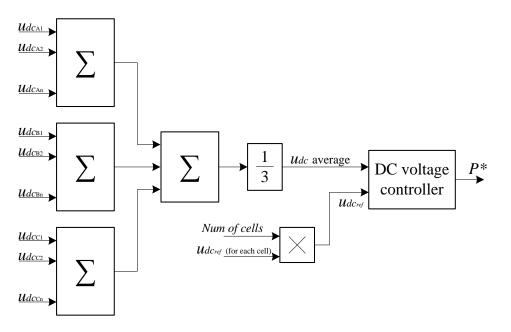

| Figure 4.29.<br>CHB c      | Block diagram of the DC voltage reference calculation for the DC voltage controller in a onverter.                                                                                                                                                                                                                             |      |

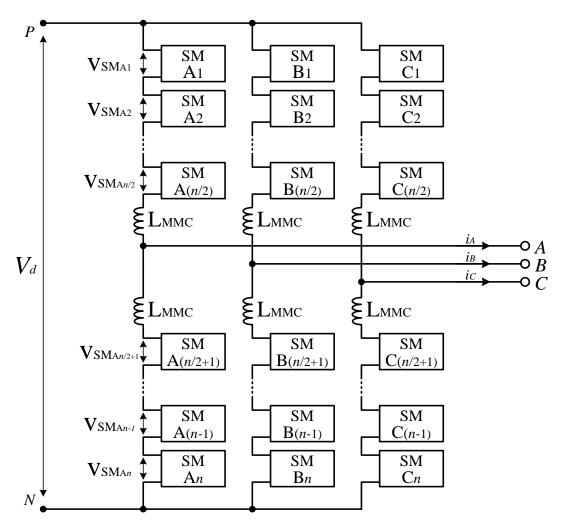

| Figure 5.1.                | General representation of Modular Multilevel converter.                                                                                                                                                                                                                                                                        | 86   |

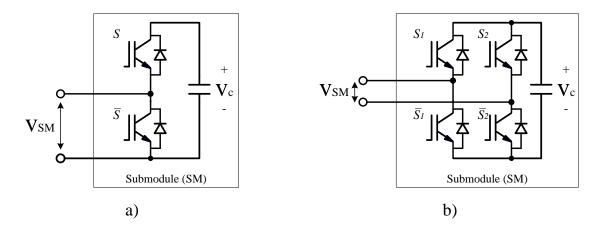

| Figure 5.2.                | Examples of half-bridge submodule a), and full-bridge submodule b).                                                                                                                                                                                                                                                            | 87   |

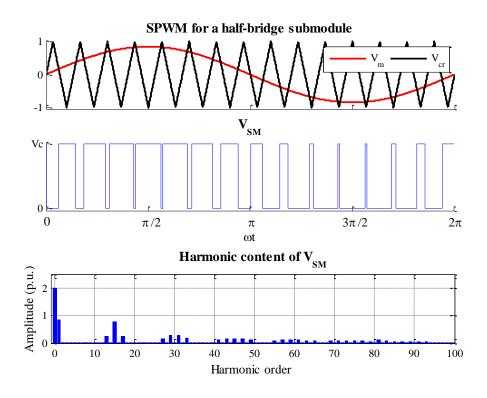

| Figure 5.3. of the o            | Representation of the SPWM signals for a half-bridge submodule, and harmonic content butput voltage obtained ( $f_m = 50$ Hz, $f_{cr} = 750$ Hz, $m_f = 15$ , $m_a = 0.85$ )    |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

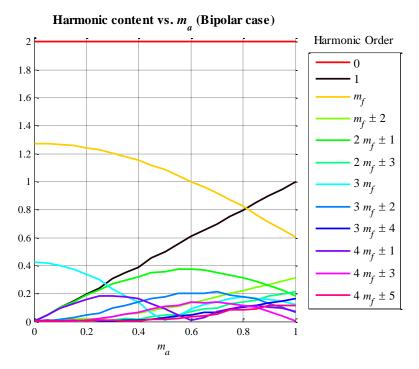

| Figure 5.4.                     | Harmonic content of the output voltage for a half-bridge submodule, as a function of the ude modulation index, m <sub>a</sub>                                                   |

| 1                               |                                                                                                                                                                                 |

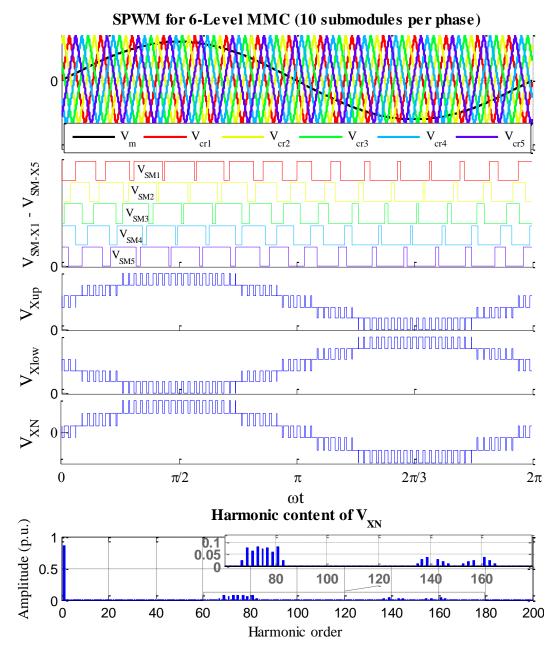

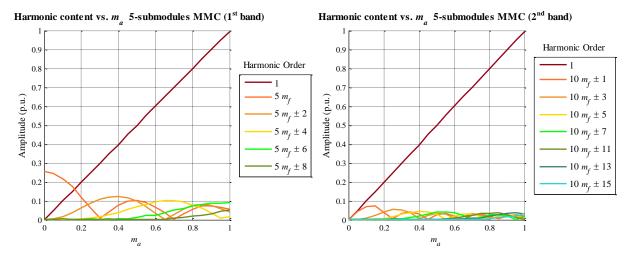

| Figure 5.5. $m_a = 0.$          | Example of SPWM scheme for a six-level MMC ( $f_m = 50$ Hz, $f_{cr} = 750$ Hz, $m_f = 15$ , .85), for a generic phase X (where X = A, B, or C)                                  |

| Figure 5.6.<br>m <sub>a</sub> . | Evolution of first (around 75 <sup>th</sup> ) and second (around 150 <sup>th</sup> ) harmonic bands as a function of                                                            |

| Figure 5.7.                     | Example of the localization of the four closest space vectors to the reference, in a space                                                                                      |

| vector                          | diagram for a 6-level converter                                                                                                                                                 |

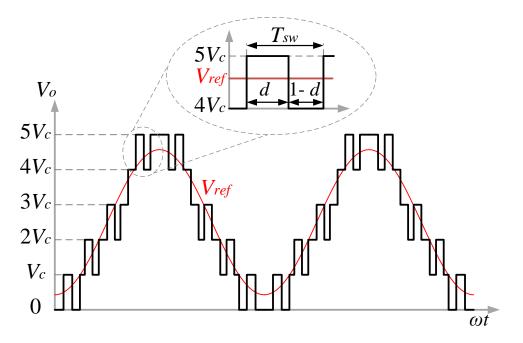

| Figure 5.8.                     | Illustration of the operation principle of Nearest Level Modulation                                                                                                             |

| Figure 5.9.                     | Voltage waveform generation of an arm in a MMC that has ten submodules per phase                                                                                                |

| _                               | NLM                                                                                                                                                                             |

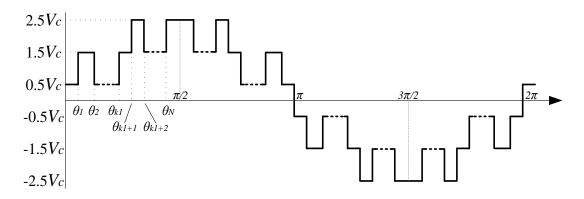

| Figure 5.10.                    | SHE waveform shape with N switching angles for a 6-level converter                                                                                                              |

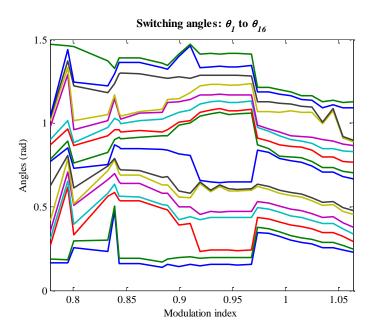

| Figure 5.11.<br>conver          | Solution set of angles for eliminating the first fifteen odd non-triple harmonics in a 6-level ter                                                                              |

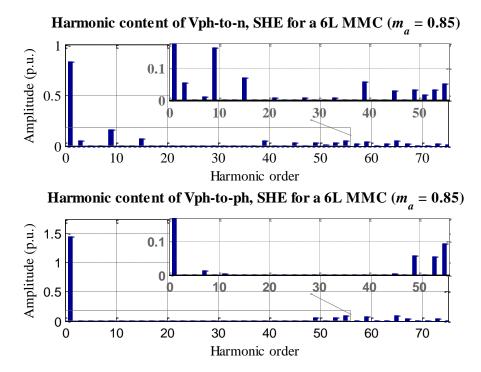

| Figure 5.12.<br>when S          | Harmonic content of the phase to neutral (up) and the phase to phase (down) voltages SHE modulation is applied to a 6-level MMC to eliminate fifteen harmonics (ma = $0.85$ )97 |

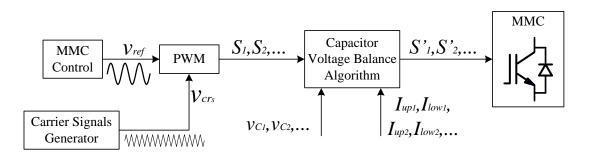

| Figure 5.13.                    | Block diagram of the application of the capacitors voltage balance method                                                                                                       |

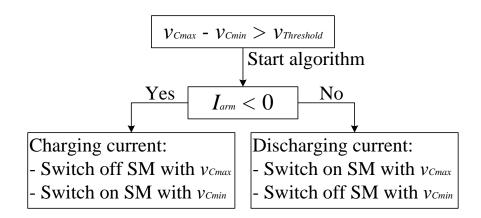

| Figure 5.14.                    | Flux diagram of the capacitors voltage balancing method                                                                                                                         |

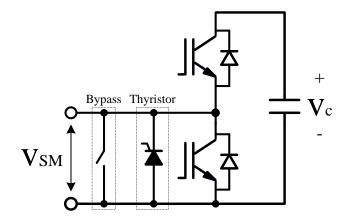

| Figure 5.15.                    | Scheme of a MMC submodule including the protection against DC fault                                                                                                             |

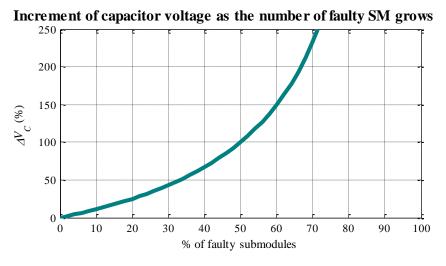

| Figure 5.16.                    | Illustration of how the increment in the capacitor voltage grows as the number of faulty                                                                                        |

| submo                           | dules in a phase increases100                                                                                                                                                   |

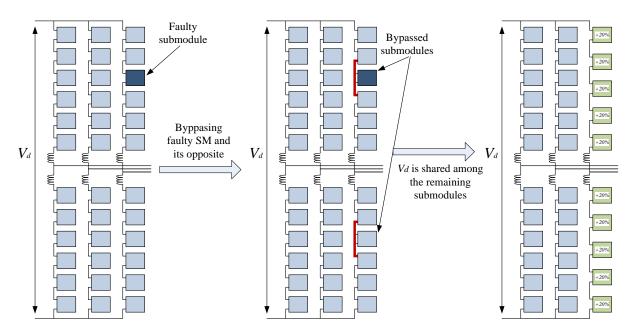

| Figure 5.17.                    | Illustration of the operation process in case of fault in a submodule100                                                                                                        |

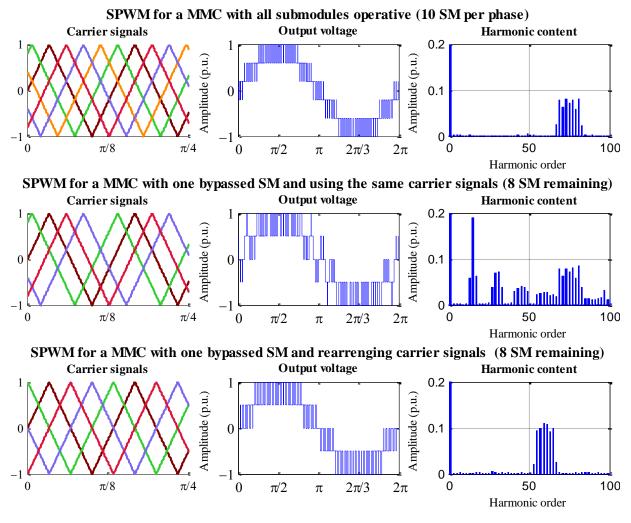

| Figure 5.18.<br>bypass          | Illustration of the rearrangement done in the carrier signals when two submodules are ed in a 10-submodules (6-levels) MMC converter                                            |

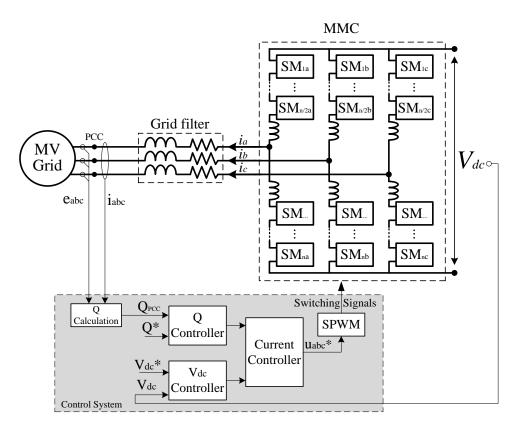

| Figure 5.19.                    | General scheme of a STATCOM system based on a MMC converter                                                                                                                     |

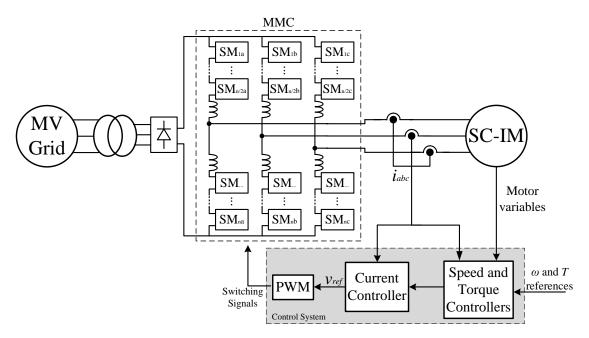

| Figure 5.20.                    | Basic scheme of motor drive using a MMC converter                                                                                                                               |

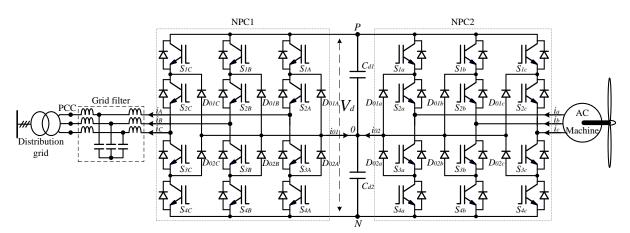

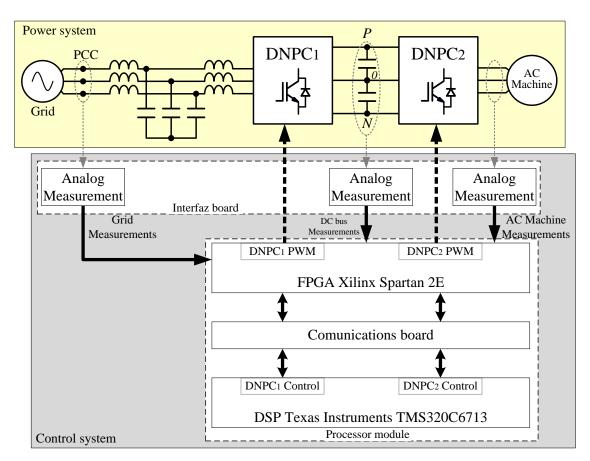

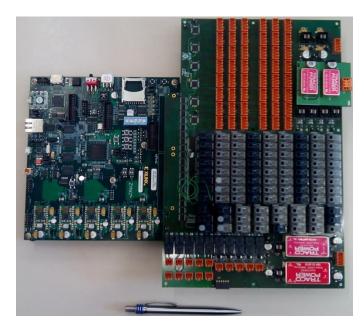

| Figure 6.1.                     | Diagram of back-to-back DNPC prototype                                                                                                                                          |

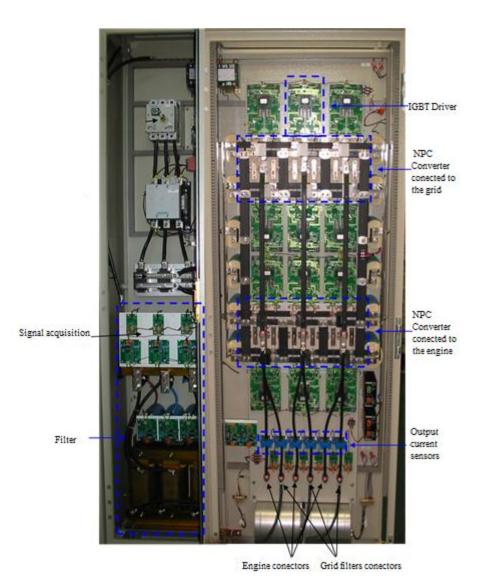

| Figure 6.2.                     | Two DNPC converters in back-to-back configuration that are in the GEISER research ory                                                                                           |

| Figure 6.3.                     | Control board for the DNPC converters, which is based in DSP+FPGA                                                                                                               |

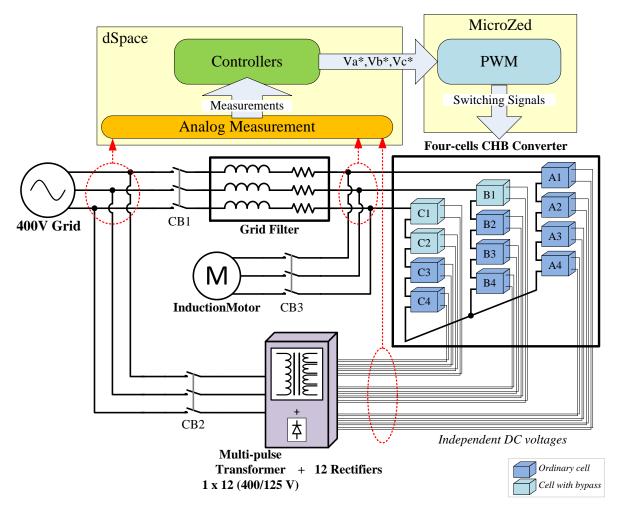

| Figure 6.4.                     | General scheme of the CHB prototype existing in GEISER research laboratory                                                                                                      |

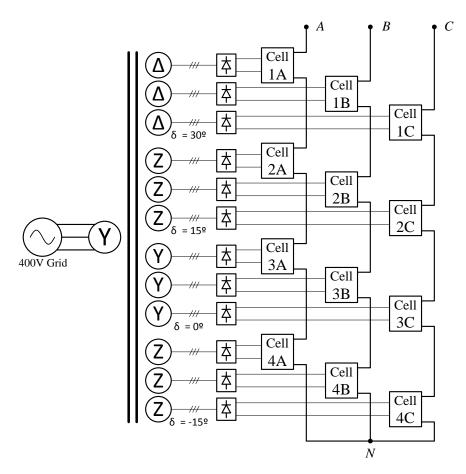

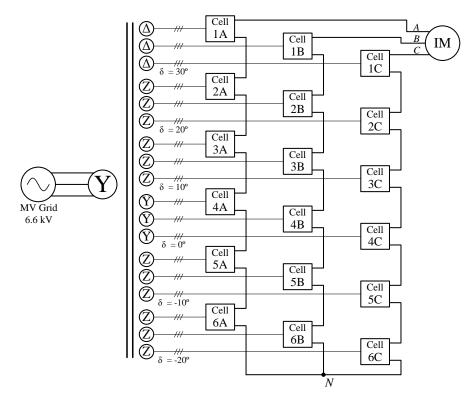

| e                               | Scheme of the CHB converter and multi-pulse transformer                                                                                                                         |

| Figure 6.5.                     | -                                                                                                                                                                               |

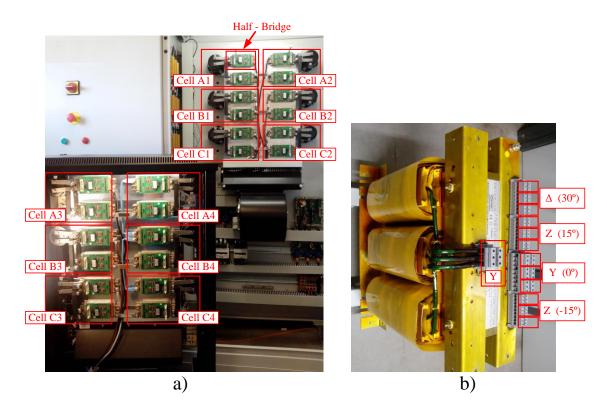

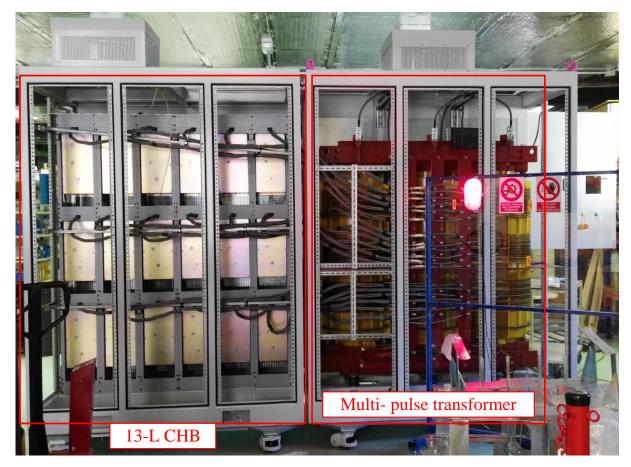

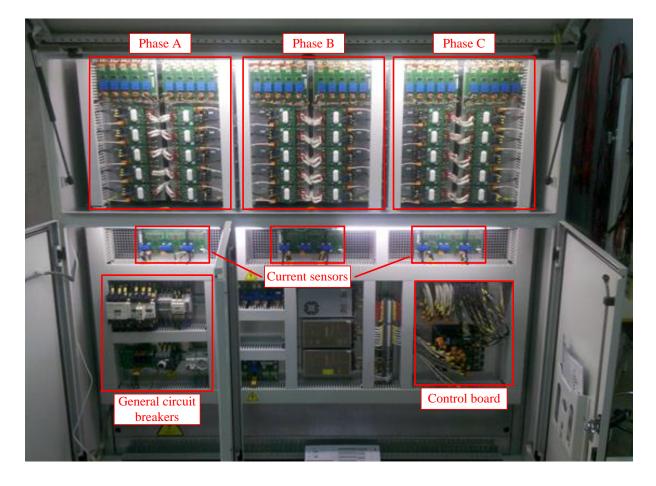

| Figure 6.6.<br>transfo          | Illustration of the 12 cells that compose the CHB converter a); and the multi-pulse rmer used to feed them b)                                                                   |

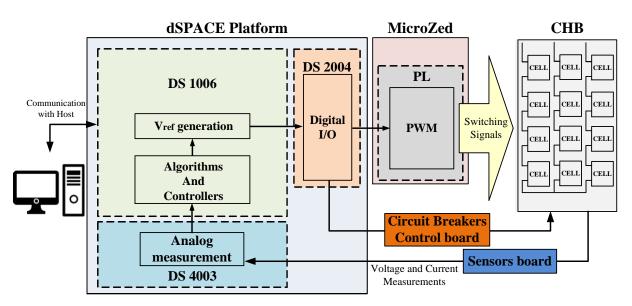

| Figure 6.7.                     | Representation of the control platform designed for the CHB converter                                                                                                           |

| Figure 6.8.                     | Illustration of SoC board based on Microzed                                                                                                                                     |

| Figure 6.9.                     | Main scheme of the six-cells thirteen-levels CHB prototype build by Sedecal Control114                                                                                          |

| Figure 6.10.                    | Illustration of the six-cells CHB converter developed by Sedecal Control                                                                                                        |

| Figure 6.11.<br>transfo         | Back view of the thirteen-levels CHB prototype: the converter (left side) and multi-pulse rmer (right side)                                                                     |

| Figure 6.12.                    | Illustration of the control system for the six-cells CHB prototype                                                                                                              |

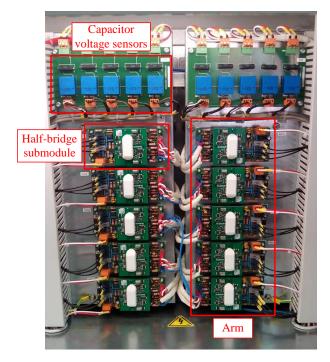

| Figure 6.13.                    | Illustration of MMC prototype                                                                                                                                                   |

| Figure 6.14.                    | Detail of one phase of the MMC prototype                                                                                                                                        |

| Figure 6.15.            | Designed hardware platform for the MMC prototype                                                                                                                                                                                               | 119    |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

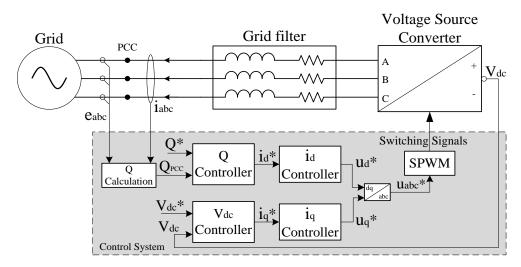

| Figure 7.1.             | General scheme for a STATCOM application.                                                                                                                                                                                                      | 123    |

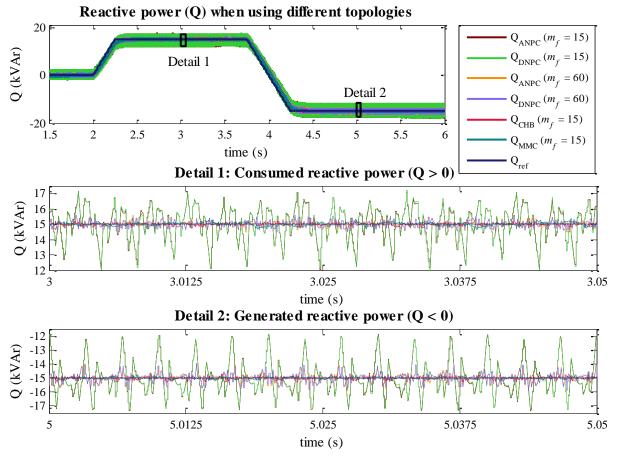

| Figure 7.2.             | Reactive power obtained after simulate the models.                                                                                                                                                                                             | 125    |

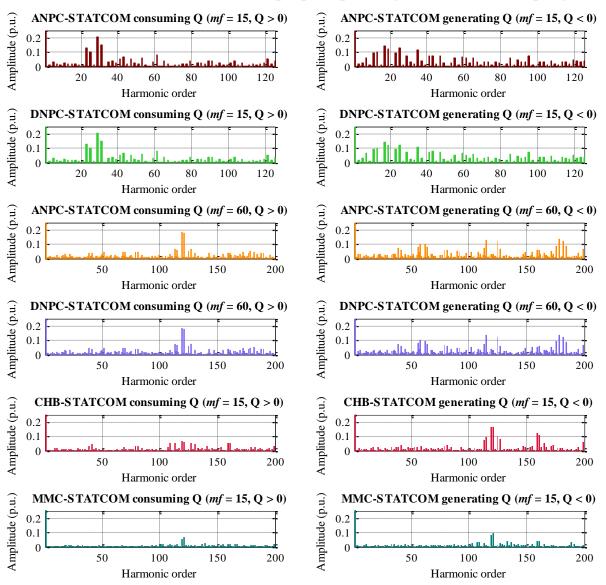

| Figure 7.3.             | Harmonic content of the converter output phase-to-phase voltage for the different models                                                                                                                                                       | 3      |

| and the                 | two possible modes of working (generation and consumption of reactive power)                                                                                                                                                                   | 126    |

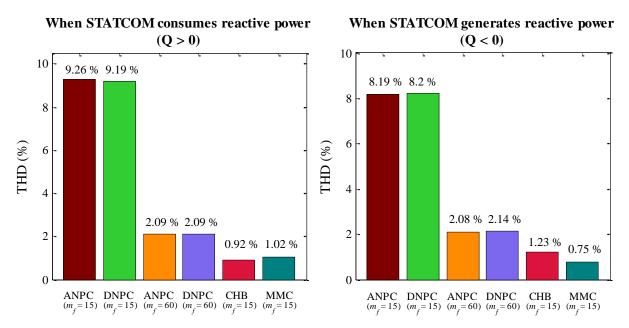

| Figure 7.4.             | THD of the PCC current depending on the used converter and the operation mode                                                                                                                                                                  | 127    |

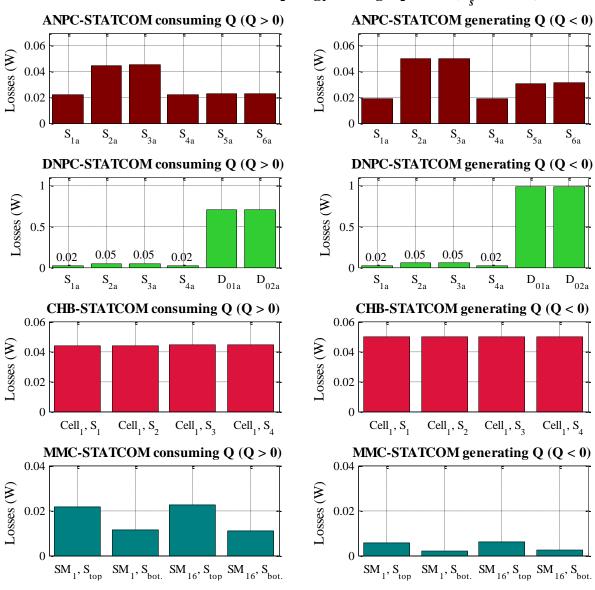

| Figure 7.5.             | Losses in the devices of each one of the studied topologies                                                                                                                                                                                    | 129    |

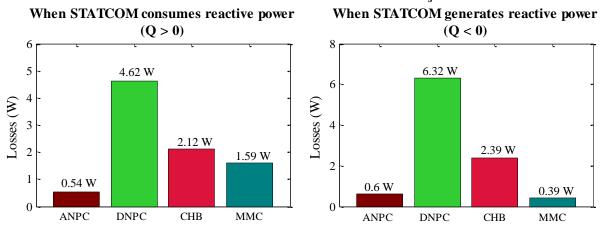

| Figure 7.6.             | Total average losses of the studied topologies during a period of the grid signal                                                                                                                                                              | 129    |

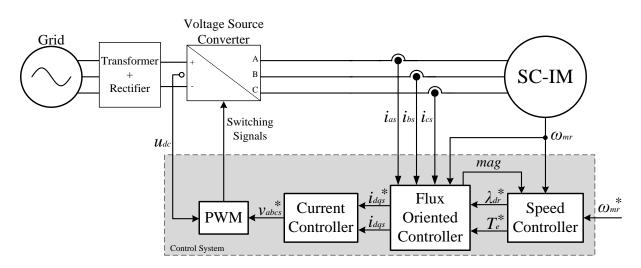

| Figure 7.7.             | General scheme for an induction motor drive controlled with indirect FOC.                                                                                                                                                                      | 130    |

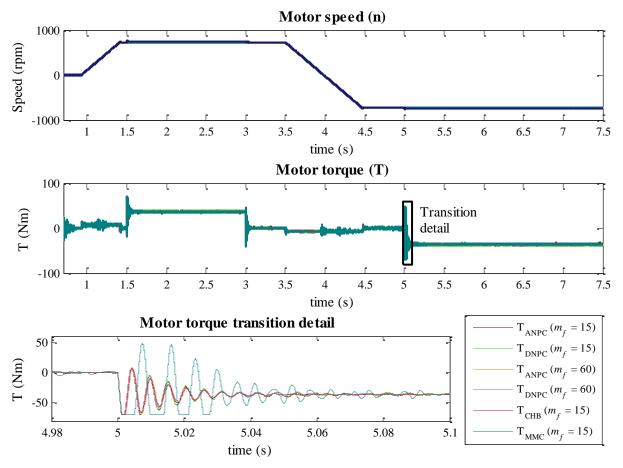

| Figure 7.8.             | Motor speed and torque obtained after running the models.                                                                                                                                                                                      | 132    |

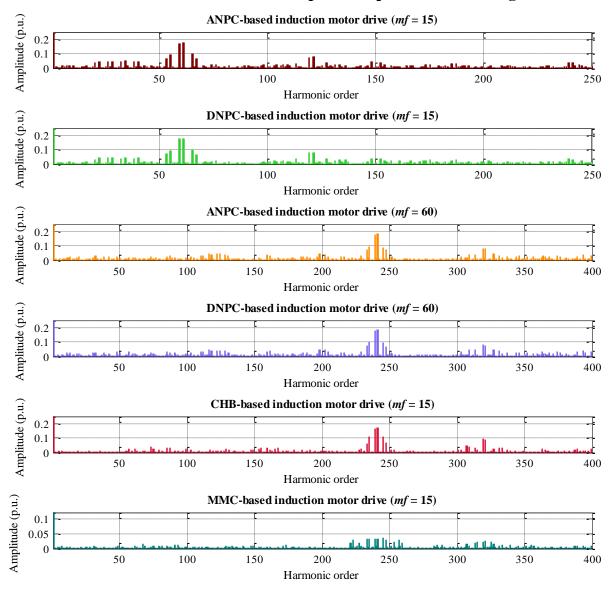

| Figure 7.9.             | Harmonic content of the motor phase-to-phase voltage for the different models                                                                                                                                                                  | 133    |

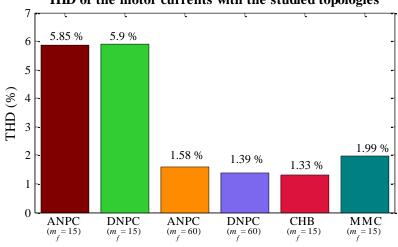

| Figure 7.10.            | THD of the motor currents for the different models                                                                                                                                                                                             | 133    |

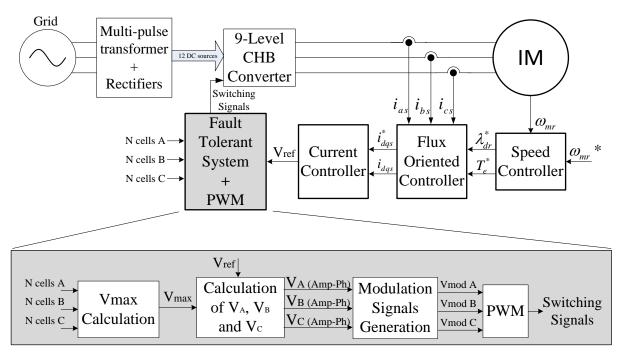

| Figure 7.11.            | Block diagram of the fault-tolerant CHB-based drive modelled                                                                                                                                                                                   | 134    |

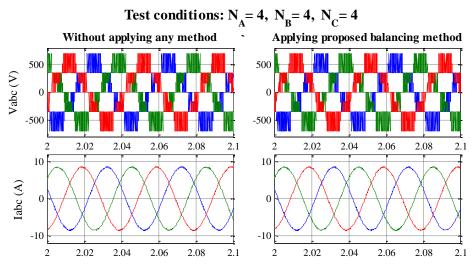

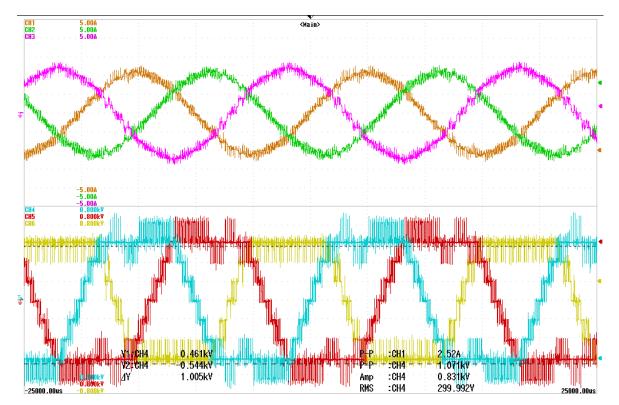

| Figure 7.12.            | Phase-to-phase voltages and currents supplied to the motor in normal operation                                                                                                                                                                 | 136    |

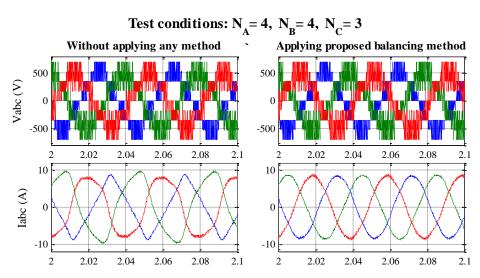

| Figure 7.13.            | Phase-to-phase voltages and currents supplied to the motor in case of fault in C1                                                                                                                                                              | 136    |

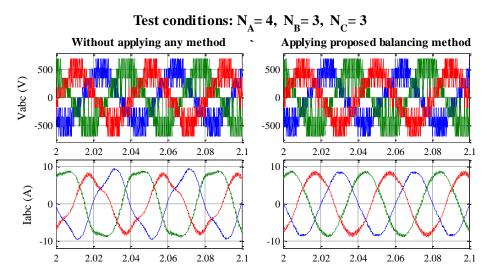

| Figure 7.14.            | Phase-to-phase voltages and currents supplied to the motor in case of fault in B1 and C1.                                                                                                                                                      | 137    |

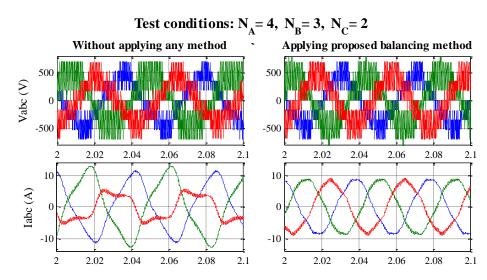

| Figure 7.15.<br>C2.     | Phase-to-phase voltages and currents supplied to the motor in case of fault in B1, C1 and                                                                                                                                                      |        |

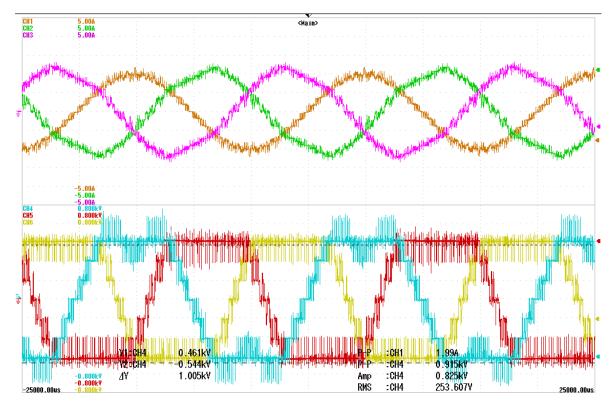

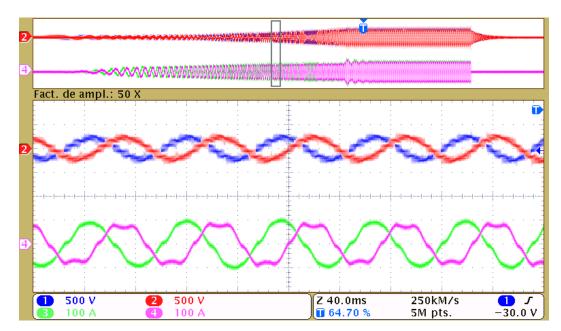

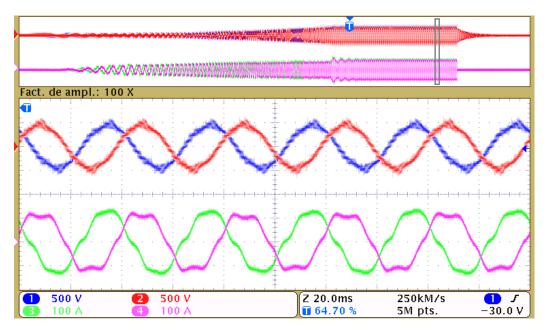

|                         | Application of the proposed neutral-shift balanced method when the CHB prototype is<br>g a resistive load of 7 kW and there is a fault in C1. The figure shows the converter currents<br>d the converter phase-to-neutral voltages (down).     | 5      |

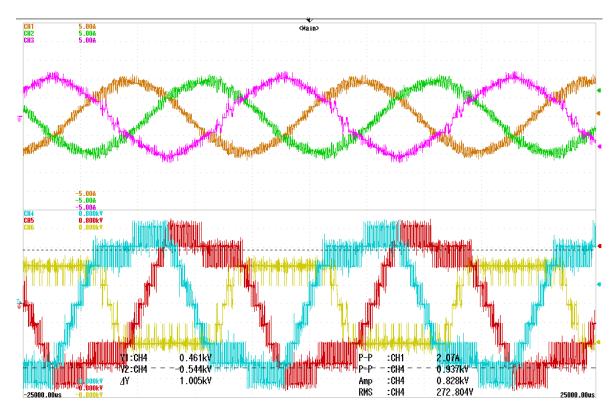

| Figure 7.17.<br>feeding | Application of the proposed neutral-shift balanced method when the CHB prototype is<br>g a resistive load of 7 kW and B1, and C1 have faults. The figure shows the converter<br>s (up) and the converter phase-to-neutral voltages (down).     | S<br>r |

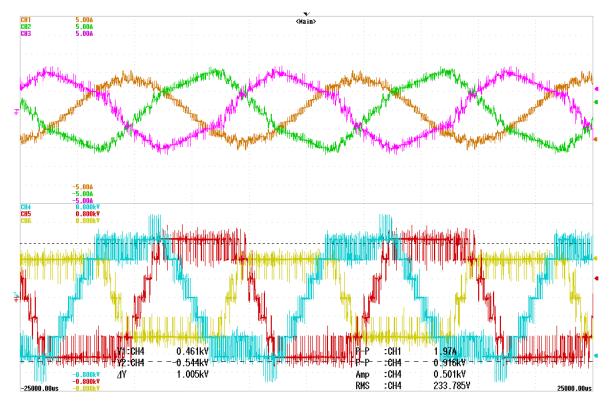

| -                       | Application of the proposed neutral-shift balanced method when the CHB prototype is<br>g a resistive load of 7 kW and C1, and C2 have faults. The figure shows the converter<br>s (up) and the converter phase-to-neutral voltages (down).     | r      |

|                         | Application of the proposed neutral-shift balanced method when the CHB prototype is<br>g a resistive load of 7 kW and B1, C1, and C2 have faults. The figure shows the converter<br>s (up) and the converter phase-to-neutral voltages (down). | r      |

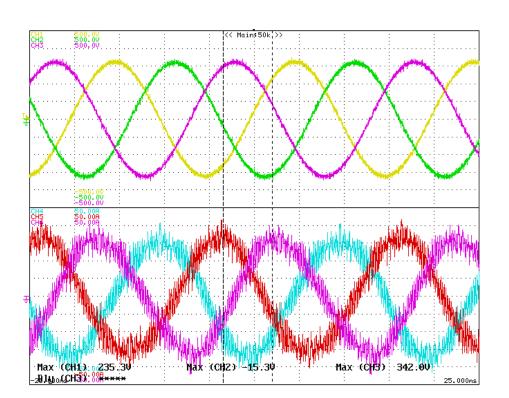

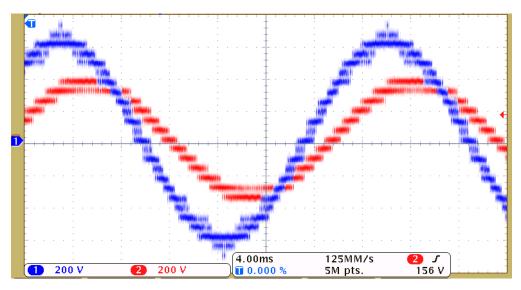

| •                       | Illustration of the PCC phase-to-phase voltages and currents in the DNPC-based                                                                                                                                                                 |        |

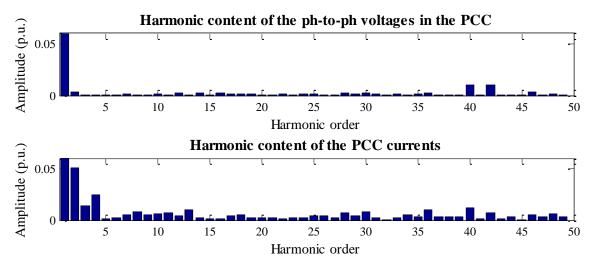

| Figure 7.21.            | Harmonic content of the PCC voltages and currents of the DNPC-based STATCOM                                                                                                                                                                    | 141    |

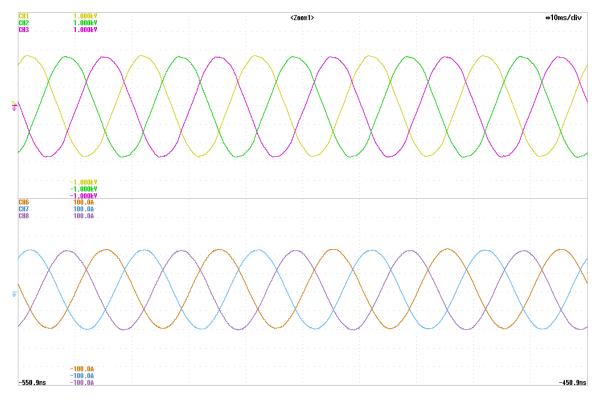

| Figure 7.22.            | Illustration of the PCC phase-to-phase voltages and currents in the MMC-based                                                                                                                                                                  |        |

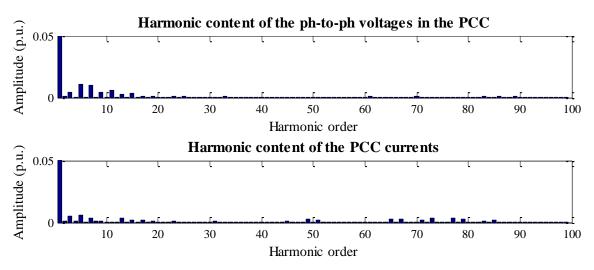

| Figure 7.23.            |                                                                                                                                                                                                                                                |        |

| Figure 7.24.            | Illustration of phase-to-phase voltage (yellow) and phase-to-neutral voltage (cyan) in the ter's output                                                                                                                                        | e      |

|                         | First example of the evolution of the phase-to-phase voltages ( $v_{AB}$ and $v_{BC}$ ) and currents                                                                                                                                           |        |

| (i <sub>A</sub> and     | $i_B$ ) when a voltage-frequency controller is applied to the described prototype                                                                                                                                                              | 143    |

| Figure 7.26.<br>current | Second example of the evolution of the phase-to-phase voltages ( $v_{AB}$ and $v_{BC}$ ) and s ( $i_A$ and $i_B$ ) when a voltage-frequency controller is applied to the described prototype                                                   |        |

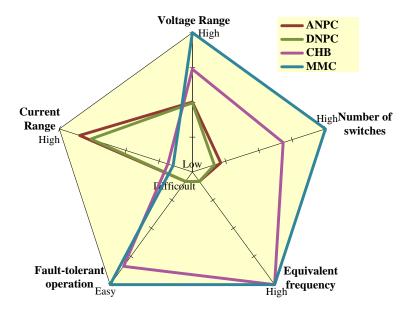

| Figure 7.27.            | Illustration of some of the main characteristics of the analyzed topologies                                                                                                                                                                    | 145    |

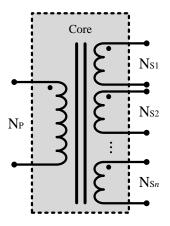

| Figure A.1.<br>and n v  | Example of monophasic multi-winding transformer with one winding in the primary side windings in the secondary side.                                                                                                                           |        |

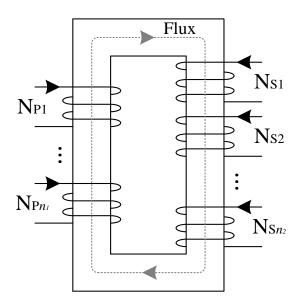

| Figure A.2. second    | Representation of the magnetic flux induced by the $n_1$ primary windings to the $n_2$ ary windings       |

|-----------------------|-----------------------------------------------------------------------------------------------------------|

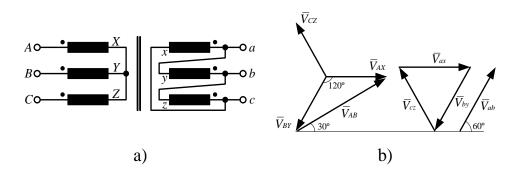

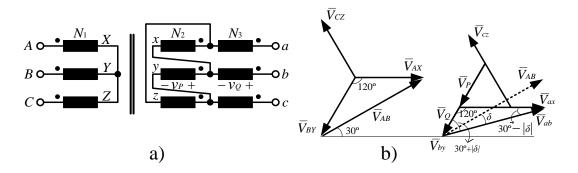

| Figure A.3.           | Representation of a wye/delta connection a), and its phasor diagram b)                                    |

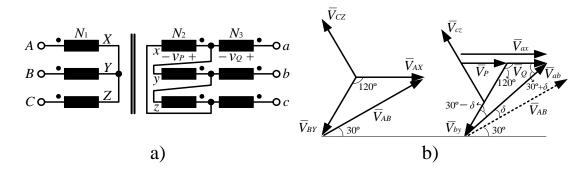

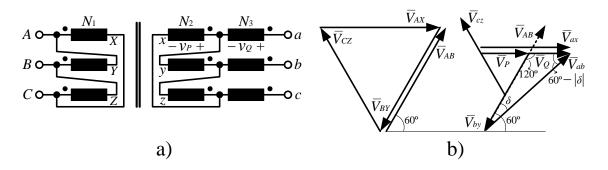

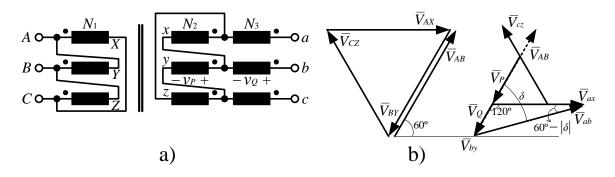

| Figure A.4.           | Representation of Y/Z-1 connection a), and its phasors diagram b)                                         |

| Figure A.5.           | Representation of connection Y/Z-2 a), and its phasors diagram b)                                         |

| Figure A.6.           | Illustration of connection $\Delta$ /Z-1 a), and its phasors diagram b)                                   |

| Figure A.7.           | Representation of connection $\Delta$ /Z-2 a), and its phasors diagram b)                                 |

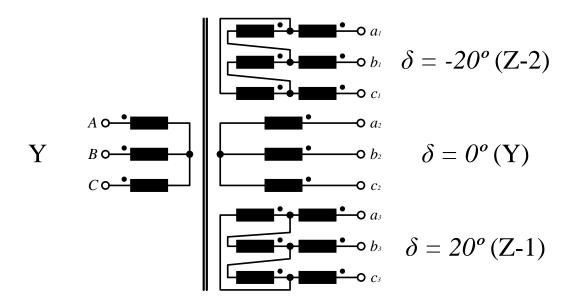

| Figure A.8.           | Example of multi-pulse transformer with three windings in the secondary side                              |

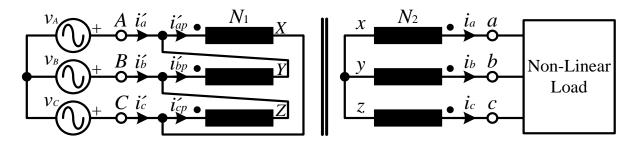

| Figure A.9.           | Delta/wye transformer fed by a balanced source and connected to a non-linear load                         |

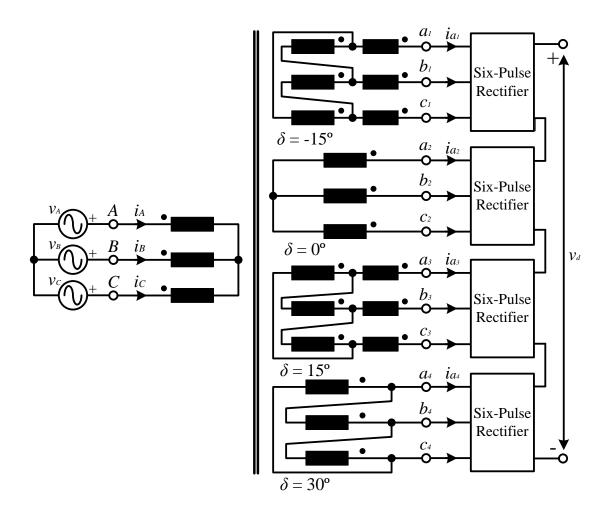

| Figure A.10.          | Example of 24-pulse rectifier to illustrate the harmonic cancellation                                     |

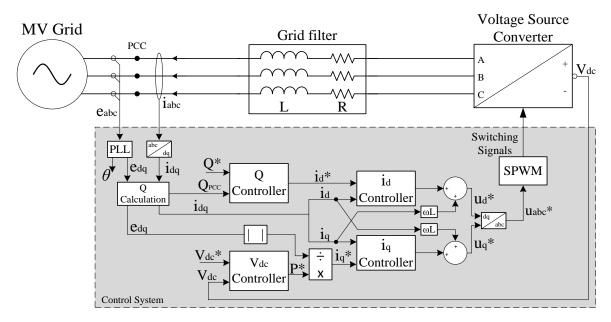

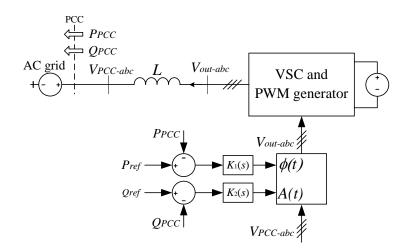

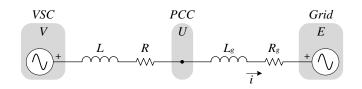

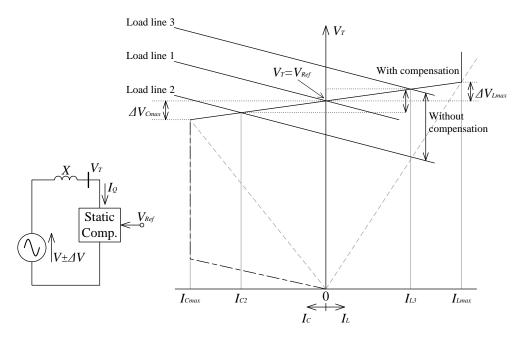

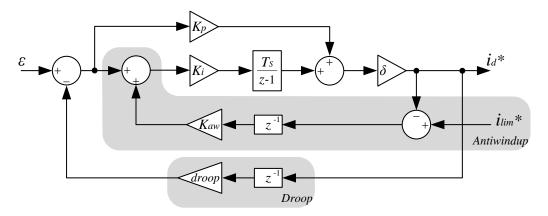

| Figure B.1.           | STATCOM control system diagram                                                                            |

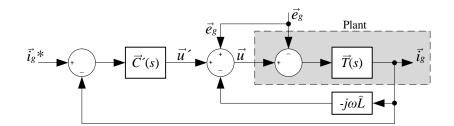

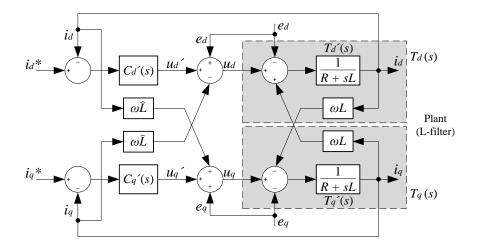

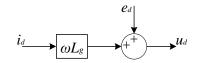

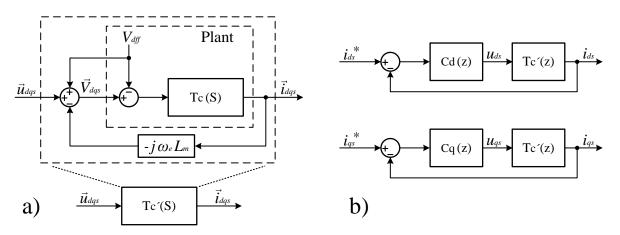

| Figure B.2. feedfor   | Current controller vector scheme with decoupling between dq-components and ward compensation of <i>eg</i> |

| Figure B.3.           | Current controllers in dq-components block diagram                                                        |

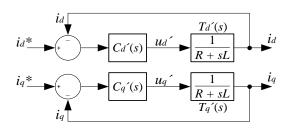

| Figure B.4.<br>comper | Scheme of current controllers with ideal decupling of dq-components and feedforward nsation               |

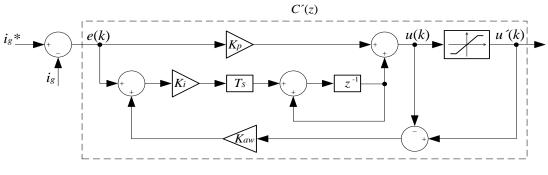

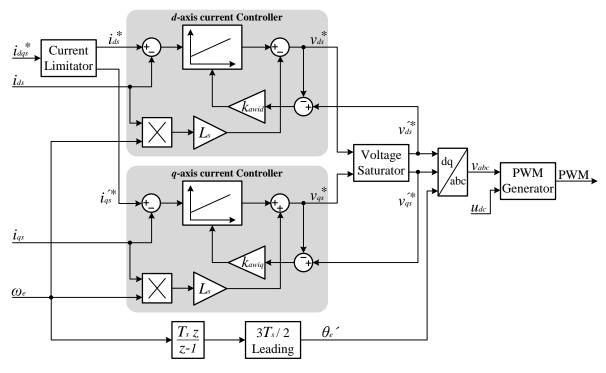

| Figure B.5.           | Current controller for the STATCOM system                                                                 |

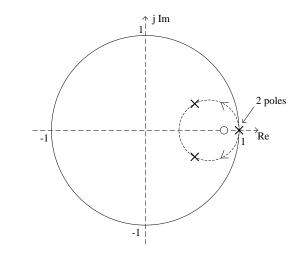

| Figure B.6.           | Root locus for the close-loop function $T'z \cdot C'z$                                                    |

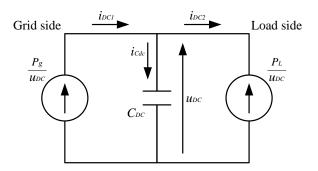

| Figure B.7.           | DC-bus Dynamic equivalent circuit                                                                         |

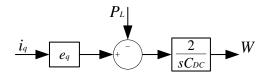

| Figure B.8.           | Approximate model of the DC-bus independent of the R <sub>L</sub>                                         |

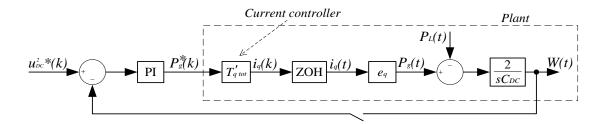

| Figure B.9.           | Control loop of $u_{DC}$ in z-domain considering the capacitor energy as control variable                 |

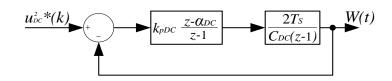

| Figure B.10.          | DC-bus controller considering the voltage and current controllers perfectly decoupled175                  |

| Figure B.11.          | STATCOM single-line diagram with the used variables for calculate the DC-bus voltage                      |

| referen               | ce                                                                                                        |

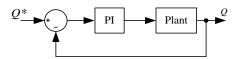

| Figure B.12.          | Reactive power controller (Q-controller)                                                                  |

| Figure B.13.          | Single-line scheme of a grid-connected STATCOM system                                                     |

| Figure B.14.          | PCC voltage controller model in dq-axis                                                                   |

| Figure B.15.          | PCC voltage regulation with a STATCOM system                                                              |

| Figure B.16.          | PCC voltage controller                                                                                    |

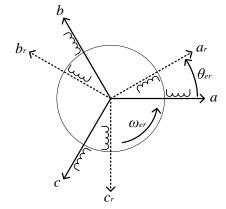

| Figure C.1.           | Rotor and stator diagram in abc-frames                                                                    |

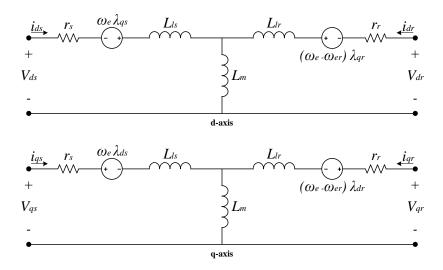

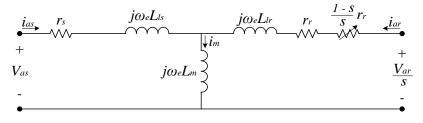

| Figure C.2.           | Induction machine equivalent circuit in synchronous reference frames                                      |

| Figure C.3.           | Induction machine a-axis equivalent circuit in steady state                                               |

| Figure C.4.           | Thevening's equivalent of the stator when the rotor windings are short-circuited188                       |

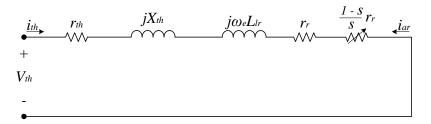

| Figure C.5.           | Average torque as a function of the slip, having constant voltage supply                                  |

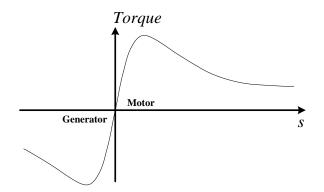

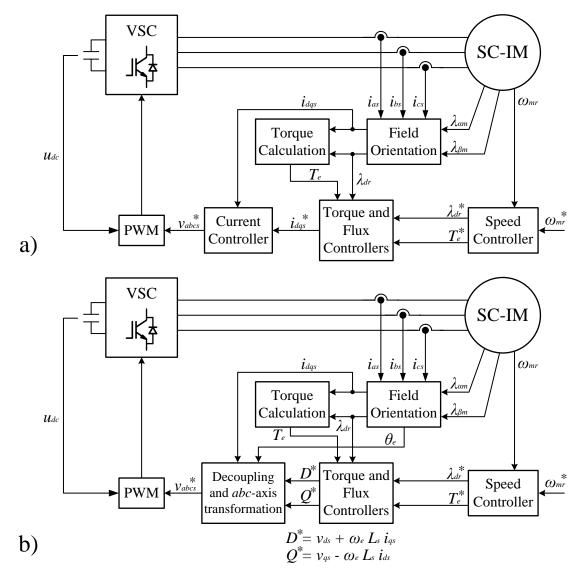

| Figure C.6.           | Direct field oriented current control (a); and Direct field oriented voltage control (b) 190              |

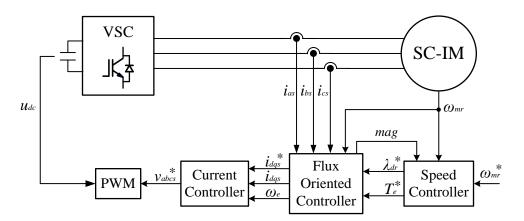

| Figure C.7.           | Indirect field oriented control                                                                           |

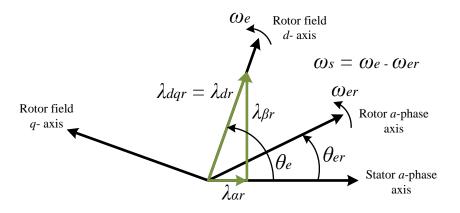

| Figure C.8.           | Flux-oriented control vector diagram                                                                      |

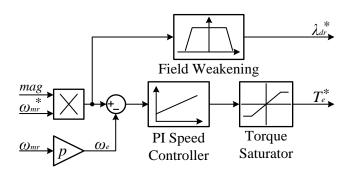

| Figure C.9.           | Speed controller block diagram                                                                            |

| Figure C.10.          | Indirect flux oriented controller block diagram                                                           |

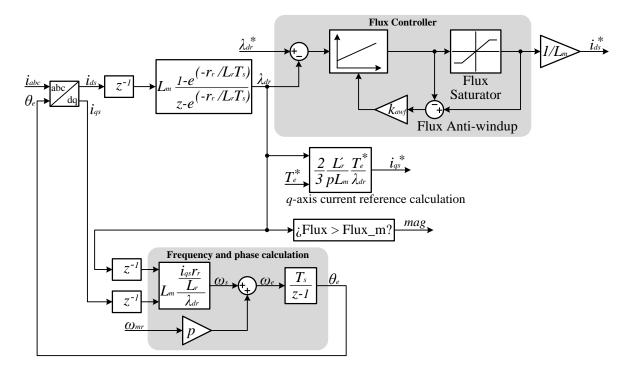

| Figure C.11.          | Current controller block diagram                                                                          |

| Figure C.12.          | Procedure to simplify the original plant (a); and independent current controllers closed                  |

#### Summary of tables

| Table | 3.1.                | Switching states for a phase of the DNPC converter (being $x = A, B, \text{ or } C$ )                                                                                                                                                                                                                                                        | 26 |

|-------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table | 3.2.                | Switching states for a phase of the active NPC converter (being $x = A, B, \text{ or } C$ ).                                                                                                                                                                                                                                                 | 27 |

| Table | 3.3.                | Conducting devices in each switching state                                                                                                                                                                                                                                                                                                   | 27 |

| Table |                     | Devices involved in the commutations between the different states of the ANPC er.                                                                                                                                                                                                                                                            |    |

| Table |                     | Switching states related to their corresponding voltage vectors for a neutral point-clamped er.                                                                                                                                                                                                                                              |    |

| Table | 3.6.                | Equivalence between switching frequency in SHE and the SPWM modulation                                                                                                                                                                                                                                                                       | 40 |

| Table | 3.7.                | Per unit ANPC losses using switching strategy proposed in [50].                                                                                                                                                                                                                                                                              | 44 |

| Table | 3.8.                | Per unit ANPC losses using switching strategy proposed in [42].                                                                                                                                                                                                                                                                              | 45 |

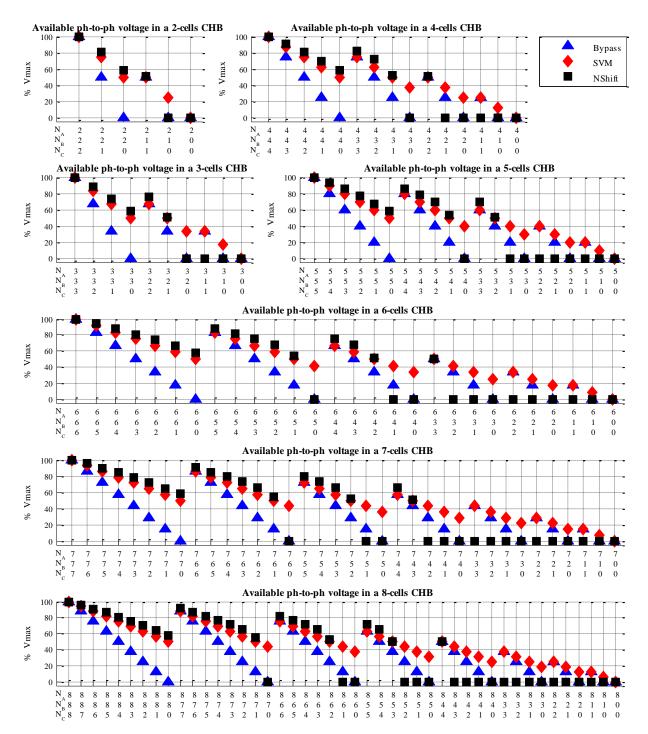

| Table | cells, fo           | Available output voltage for the CHB converter depending on the number of bypassed or converters with 2, 3, 4, 5, 6, 7 and 8 cells per phase, when the cells in the same level are ed too.                                                                                                                                                   |    |

| Table | 4.2.<br>of fault    | Available phase-to-phase output voltage for the CHB converter depending on the number y cells, for converters with 2, 3, 4, 5, 6, 7 and 8 cells per phase, when redundant switching re used.                                                                                                                                                 |    |

| Table | of fault            | Available phase-to-phase output voltage for the CHB converter depending on the number ty cells, for converters with 2, 3, 4, 5, 6, 7 and 8 cells per phase, when neutral-shift ng method is used.                                                                                                                                            |    |

| Table | depender<br>and 8 c | Comparison of the available phase-to-phase output voltage for the CHB converter ing on the number of available cells ( $N_A$ , $N_B$ , and $N_C$ ), for converters with 2, 3, 4, 5, 6, 7 ells per phase, when the explained methods are used: bypassing the cells in the same level, ne redundant states of SVM, and applying neutral-shift. |    |

| Table | 6.1.                | Main characteristics of the DNPC prototype power system1                                                                                                                                                                                                                                                                                     | 07 |

| Table | 6.2.                | Tasks distribution between DSP and FPGA.                                                                                                                                                                                                                                                                                                     | 08 |

| Table | 6.3.                | H-bridge cells main features                                                                                                                                                                                                                                                                                                                 | 10 |

| Table | 6.4.                | Characteristics of multi-pulse transformer used to feed CHB converter 1                                                                                                                                                                                                                                                                      | 11 |

| Table | 6.5.                | 18-secondary windings multi-pulse transformer parameters 1                                                                                                                                                                                                                                                                                   | 15 |

| Table | 6.6.                | MMC prototype main parameters 1                                                                                                                                                                                                                                                                                                              | 17 |

| Table | 7.1.                | General comparison between the studied topologies1                                                                                                                                                                                                                                                                                           | 22 |

| Table | 7.2.                | Main data for the STATCOM models                                                                                                                                                                                                                                                                                                             | 24 |

| Table | 7.3.                | Reactive power maximum ripple using the different models (kVAr) 1                                                                                                                                                                                                                                                                            | 25 |

| Table | 7.4.                | Theoretical place where the voltage harmonics are placed for each topology 1                                                                                                                                                                                                                                                                 |    |

| Table | 7.5.                | Main data for the drive models                                                                                                                                                                                                                                                                                                               | 31 |

| Table | 7.6.                | Main data of the fault-tolerant CHB-based drive with indirect FOC control                                                                                                                                                                                                                                                                    | 35 |

| Table | 7.7.                | Quantification of the voltage and current imbalance for the cases of normal operation, and                                                                                                                                                                                                                                                   |    |

|       | for the             | cases of fault in C1, in B1 and C1, and in case of fault in B1, C1 and C2 1                                                                                                                                                                                                                                                                  | 36 |

| Table |                     | Voltage imbalance quantification of the balancing method applied to the CHB converter                                                                                                                                                                                                                                                        |    |

|       |                     | ds a 7 kW resistive load1                                                                                                                                                                                                                                                                                                                    |    |

| Table | A.1.                | Examples of multi-pulse Transformers connections 1                                                                                                                                                                                                                                                                                           |    |

| Table | B.1.                | Main parameters of the controllers in the STATCOM system 1                                                                                                                                                                                                                                                                                   | 67 |

A Sofía y Marisa, por llegar a mí para ser mis salvadoras, mi razón de vivir, mi alegría.

A Ti, que ya no puedes leer estas líneas. No te fuiste del todo, sigues en mí.

# **CONTENTS**

| Abstract    |                                               | i    |

|-------------|-----------------------------------------------|------|

| Resumen     |                                               | iii  |

| Agradecimie | entos                                         | v    |

| Glossary    |                                               | .vii |

| Summary of  | figures and tables                            | ix   |

| Contents    |                                               | 1    |

| Chapter 1:  | Introduction                                  | 5    |

| 1.1. Introd | duction                                       | 5    |

| 1.2. Objec  | ctives of this thesis                         | . 10 |

| 1.3. Struc  | ture of this Thesis                           | . 11 |

| 1.4. Proje  | cts related with this Thesis                  | . 12 |

| 1.5. Relat  | ed Papers                                     | . 12 |

| Chapter 2:  | Background                                    | .17  |

| 2.1. Over   | view                                          | . 17 |

| 2.1.1. N    | Aultilevel topologies overview                | 17   |

| 2.1.2. N    | Modulation techniques background              | 21   |

| 2.1.3. F    | Fault-tolerant operation background           | 23   |

| 2.2. Sumr   | nary of contributions                         | . 24 |

| Chapter 3:  | Neutral Point-Clamped topologies: DNPC - ANPC | .25  |

| 3.1. Торо   | logies description                            | . 25 |

| 3.1.1. I    | Diode NPC                                     | 26   |

| 3.1.2. Active NPC                                                              | .26 |

|--------------------------------------------------------------------------------|-----|

| 3.2. Modulation methods                                                        | 30  |

| 3.2.1. Sinusoidal Pulse-Width Modulation for NPC converters                    | .30 |

| 3.2.2. Space Vector Modulation for NPC converters                              | .35 |

| 3.2.3. Selective Harmonic Elimination for NPC converters                       | .37 |

| 3.2.3.1. Carrier-based selective harmonic elimination                          | .41 |

| 3.2.4. Zero states switching selection                                         | .43 |

| 3.3. Applications for NPC converters                                           | 46  |

| 3.3.1. Distributed power generation                                            | .46 |

| 3.3.2. Power quality applications                                              | .47 |

| 3.3.3. Drive applications                                                      | .47 |

| 3.3.4. Peculiarities of neutral point-clamped topologies                       | .47 |

| Chapter 4: Cascaded H-Bridge converter                                         | 51  |

| 4.1. Topology description                                                      | 51  |

| 4.2. Modulation methods                                                        | 53  |

| 4.2.1. Sinusoidal Pulse-Width Modulation for CHB converters                    | .53 |

| 4.2.1.1. Pulse-Width Modulation for an H-bridge                                | .54 |

| 4.2.1.2. Pulse-Width Modulation for a set of H-bridge cells cascaded-connected | .57 |

| 4.2.2. Space Vector Modulation                                                 | .60 |

| 4.2.3. Selective Harmonic Elimination for CHB converters                       | .61 |

| 4.2.3.1. Stair-case SHE for CHB converters                                     | .62 |

| 4.3. CHB operation with faulty cells                                           | 65  |

| 4.3.1. Bypassing cells of the same level                                       | .66 |

| 4.3.2. Space Vector Modulation with redundant switching states                 | .67 |

| 4.3.3. Using variable DC voltages                                              | .70 |

| 4.3.4. Neutral shift method                                                    | .71 |

| 4.3.5. Comparison between the explained balancing methods                      | .76 |

| 4.4. Applications for CHB converters                                           | 81  |

| 4.4.1. Drive applications                                                      | .82 |

| 4.4.2. Power quality applications                                              | .82 |