Universidad de Alcalá Escuela Politécnica Superior

Máster Universitario en Ingeniería Industrial

Trabajo Fin de Máster

Control Analysis and Design of Medium Voltage Converter with Multirate Techniques

# ESCUELA POLITECNICA

SUPERIOR

Autor: Javier Serrano Delgado

**Tutor/es:** Emilio José Bueno Peña Mario Rizo Morente

2018

#### UNIVERSIDAD DE ALCALÁ Escuela Politécnica Superior

#### Máster Universitario en Ingeniería Industrial

Trabajo Fin de Máster

#### Control Analysis and Design of Medium Voltage Converter with Multirate Techniques

| Autor:    | Javier Serrano Delgado |

|-----------|------------------------|

| Tutor/es: | Emilio José Bueno Peña |

|           | Mario Rizo Morente     |

#### TRIBUNAL:

Presidente: Santiago Cóbreces Álvarez

Vocal 1º: Manuel Roza Zurera

Vocal 2º: Emilio José Bueno Peña

FECHA: 11/09/2018

### Acknowledgements

Las casualidades no existen, solo creo en las probabilidades y, por eso, la consecución de este objetivo ha sido gracias al apoyo de mi familia, pareja y amigos. Así que, por un lado, no quiero dejar de agradecer a mis padres, Fernando y Victoria, todo lo que nos han aportado a mis hermanos y a mí, destacando dos cosas fundamentales: cariño y valores. También a Jésica, por ser mi mejor amiga y compañera de vida, con la que puedo compartir mis penas y glorias porque siempre está ahí. Y a mis amigos, Álvaro, Sergio, Ricardo y Jairo, por darme buenos momentos desde que tengo uso de razón, los cuales han permitido a mi cabeza abandonar los compromisos durante un par de horas.

Por otro lado, me gustaría agradecer a Emilio y Mario su tutela, porque, aunque el tema que hemos propuesto sea complicado, me han apoyado y he alcanzado los objetivos. Espero que este sea el comienzo de nuevos e interesantes proyectos.

También agradecer a los compañeros de despacho, Javier y Marco, sus consejos y conversación durante este tiempo. A los que además deseo lo mejor en su futuro profesional.

Gracias a todos ellos tengo un equilibrio vital que me permite vivir sin miedo a las aspiraciones futuras.

"Vivir es enfrentar un problema tras otro. La forma en que lo encaras hace la diferencia"

Benjamin Franklin

# Contents

| List of figures                                            | vii  |

|------------------------------------------------------------|------|

| List of tables                                             | xiii |

| List of acronyms                                           | xv   |

| Resumen                                                    | xvii |

| Abstract                                                   | xix  |

| Extended abstract                                          |      |

| Chapter 1. Introduction                                    |      |

| 1.1. Motivation                                            |      |

| 1.1.1. Flexible AC Transmission System (FACTS) controllers |      |

| 1.1.2. Industrial applications                             | 5    |

| 1.1.3. Power semiconductor devices                         |      |

| 1.1.4. Multirate approach                                  | 9    |

| 1.2. Power converter topology                              |      |

| 1.2.1. Classification                                      |      |

| 1.2.2. Diode Neutral Point Clamped VSC                     |      |

| 1.3. Practical objectives                                  |      |

| 1.4. Structure of this work                                |      |

| Chapter 2. Theoretical study                               | 15   |

| 2.1. Introduction                                          |      |

| 2.2. State of the art                                      |      |

| 2.2.1. Multirate bases                                     |      |

| 2.2.1.1. Definitions                                       |      |

| 2.2.1.2. Background                                        |      |

| 2.2.2. Modulation techniques                               |      |

| 2.2.2.1. Background                                        |      |

| 2.2.2.2. Sinusoidal Pulse-Width Modulation                 |      |

| 2.2.2.3. Digital SPWM                                      |      |

| 2.2.2.4. Selective Harmonic Elimination                        | 28   |

|----------------------------------------------------------------|------|

| 2.2.3. Modelling of the digital SPWM                           | . 31 |

| 2.2.3.1. Small signal modelling of regular sampled PWM         | 31   |

| 2.2.3.2. Multisampling                                         | 35   |

| 2.2.3.3. ZOH model for DSPWM                                   | 40   |

| 2.2.3.4. Continuous-time modelling of DSPWM                    | 41   |

| 2.2.3.5. Discrete-time modelling of DSPWM                      | 45   |

| 2.2.4. Examples of multirate applications in power electronics | . 49 |

| 2.2.4.1. Multirate PLL                                         | 49   |

| 2.2.4.2. Multirate repetitive control                          | 51   |

| 2.3. Used multirate techniques                                 | . 54 |

| 2.3.1. Internal representation modelling                       | . 54 |

| 2.3.1.1. Definitions                                           | 54   |

| 2.3.1.2. Recurrence Laws                                       | 56   |

| 2.3.2. External representation modelling                       | . 58 |

| 2.3.2.1. Definitions                                           | 59   |

| 2.3.2.2. Polynomial $W(z_N)$ and operator $z_N^{-i}$           | 60   |

| 2.3.2.3. Pole and zero map at fast rate                        | 61   |

| 2.4. Conclusions                                               | . 62 |

| Chapter 3. Modelling and multirate applications                | 65   |

| 3.1. Introduction                                              | . 65 |

| 3.2. Voltage Source Converter modelling                        | . 65 |

| 3.2.1. Definitions of the current dynamics model               | . 65 |

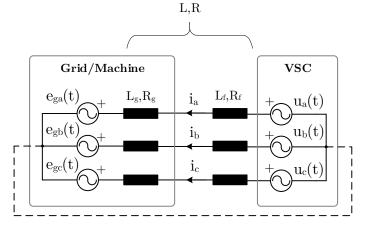

| 3.2.2. L-filter model                                          | . 67 |

| 3.2.2.1. Stationary reference frame                            | 68   |

| 3.2.2.2. Rotating reference frame                              | 68   |

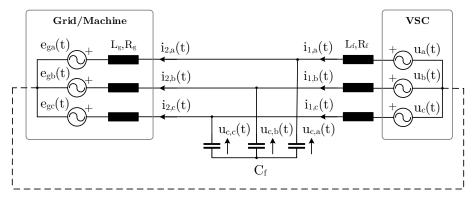

| 3.2.3. LC-filter model                                         | . 69 |

| 3.2.3.1. Stationary reference frame                            | 70   |

| 3.2.3.2. Rotating reference frame                              | 71   |

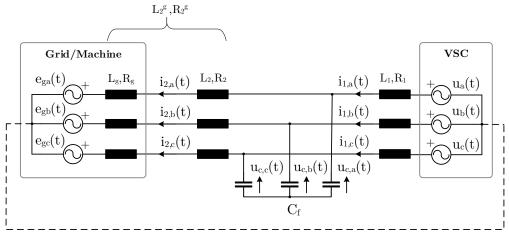

| 3.2.4. LCL-filter model                                        | . 72 |

| 3.2.5. Discretization                                          | . 73 |

| 3.3. Multirate applications                                    | . 75 |

| 3.3.1. Purpose                                                 | . 75 |

| 3.3.2. Reduction of the DSPWM delay               |    |

|---------------------------------------------------|----|

| 3.3.2.1. Phase advancing compensation             |    |

| 3.3.2.2. Extrapolation of the modulating signal   |    |

| 3.3.3. Extrapolation for SHE modulation           |    |

| 3.3.3.1. Definitions                              |    |

| 3.3.3.2. Polynomial extrapolation                 |    |

| 3.3.3.3. Sinusoidal extrapolation                 |    |

| 3.3.4. Hierarchical control structures            |    |

| 3.3.4.1. Possibilities                            |    |

| 3.3.4.2. Microgrids                               |    |

| 3.3.4.3. Multirate application                    |    |

| 3.3.5. Other multirate possibilities              |    |

| 3.3.5.1. Fast power semiconductor devices         |    |

| 3.3.5.2. Computational burden of extra algorithms |    |

| 3.4. Conclusions                                  |    |

| Chapter 4. Multirate controllers                  | 91 |

| 4.1. Introduction                                 |    |

| 4.2. Proposed single-rate controllers             |    |

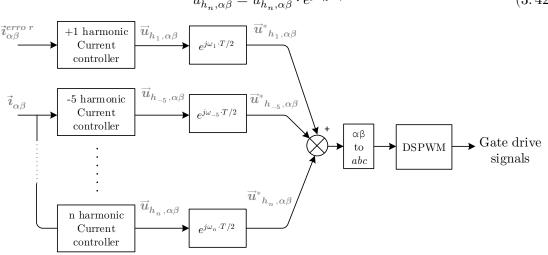

| 4.2.1. Stationary reference frame                 |    |

| 4.2.2. Rotating reference frame                   |    |

| 4.3. Time-domain multirate analysis               |    |

| 4.3.1. Definitions                                |    |

| 4.3.2. Stationary reference frame                 |    |

| 4.3.3. Rotating reference frame                   |    |

| 4.3.4. Detailed model                             |    |

| 4.3.5. Discussion                                 |    |

| 4.4. Model-based multirate controller             |    |

| 4.4.1. Definitions                                |    |

| 4.4.1.1. Basic multirate operations               |    |

| 4.4.1.2. Plant                                    |    |

| 4.4.1.3. Closed-loop multirate control            |    |

| 4.4.1.4. Controller design                        |    |

| 4.4.2. Stationary reference frame                 |    |

| 4.4.3. Rotating reference frame               | 117            |

|-----------------------------------------------|----------------|

| 4.4.4. Detailed model                         |                |

| 4.4.5. Discussion                             |                |

| 4.5. Conclusions                              |                |

| Chapter 5. Conclusions and future works       |                |

| 5.1. Conclusions                              |                |

| 5.2. Future works                             |                |

| Chapter 6. Budget                             |                |

| 6.1. Material cost                            |                |

| 6.2. Professional fees                        |                |

| 6.3. Total cost                               |                |

| Appendix A. Multirate modelling techniques b  | bases133       |

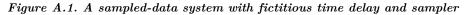

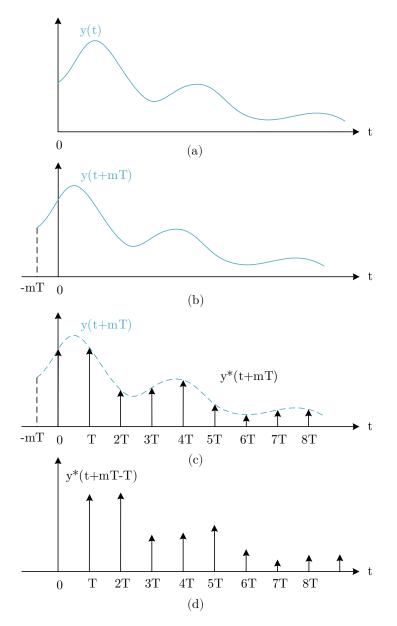

| A.1. Signals between sampling instants        |                |

| A.1.1. The delayed Z-transform                |                |

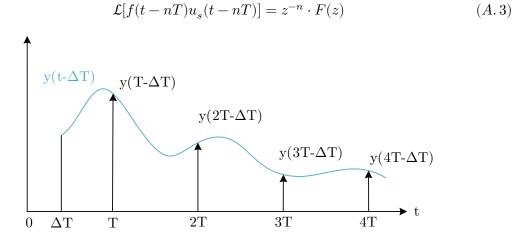

| A.1.2. The modified Z-transform               |                |

| A.1.3. The inverse Modified Z-transform       |                |

| A.1.4. The modified Z-transfer function       |                |

| A.1.5. Example                                |                |

| A.2. Multirate Sampler-Decomposition method   | 141            |

| Appendix B. Vector representation of three-p  | hase variables |

| •••••                                         |                |

| B.1. Spatial vector                           |                |

| B.2. Stationary $\alpha\beta$ reference frame |                |

| B.3. Rotating $dq$ reference frame            |                |

| Appendix C. VSC basic control loops           | 151            |

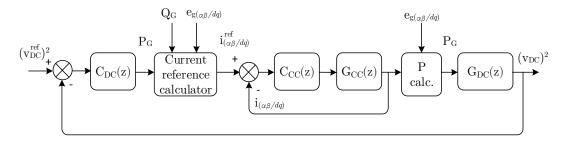

| C.1. DC-bus voltage control                   |                |

| C.1.1. DC-bus Modelling                       |                |

| C.1.2. DC-bus Controller                      |                |

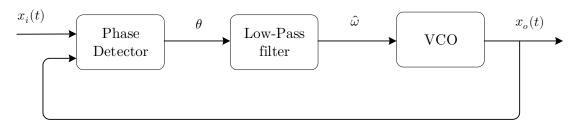

| C.2. Grid synchronization                     |                |

| C.2.1. Objectives                             |                |

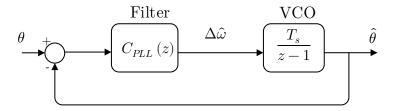

| C.2.2. Phase-Locked Loop (PLL)                |                |

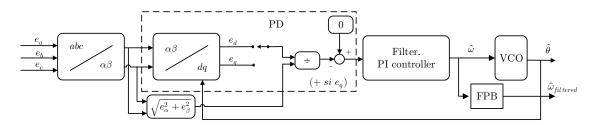

| C.2.3. SRF-PLL controller |  |

|---------------------------|--|

| References                |  |

### LIST OF FIGURES

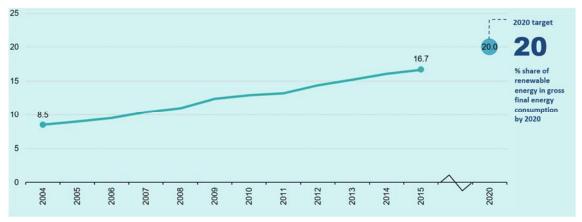

| Figure 1.1. Share of renewable energy in gross final energy consumption. Source:<br>Eurostat                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

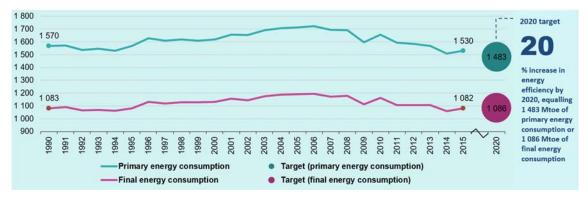

| Figure 1.2. Primary energy consumption and final energy consumption. Source:<br>Eurostat                                                                                                                                                                  |

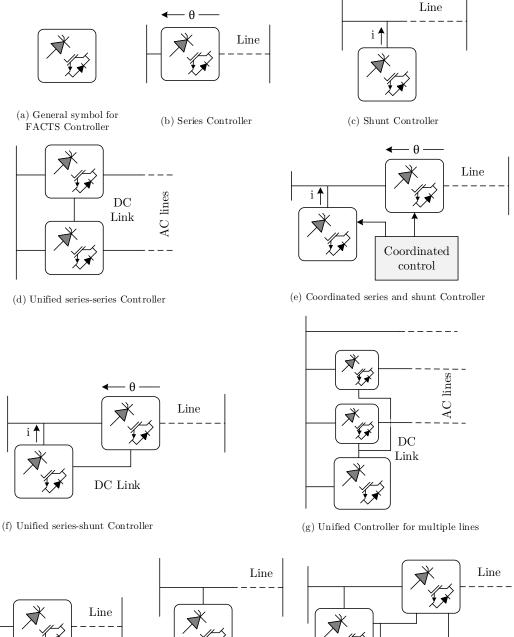

| FIGURE 1.3. BASIC TYPES OF FACTS CONTROLLERS                                                                                                                                                                                                              |

| FIGURE 1.4. SINAMICS SM120 CM MEDIUM VOLTAGE DRIVE. SOURCE: SIEMENS WEB                                                                                                                                                                                   |

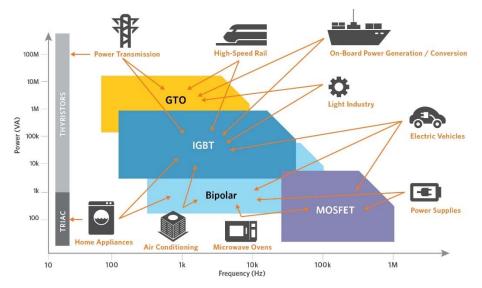

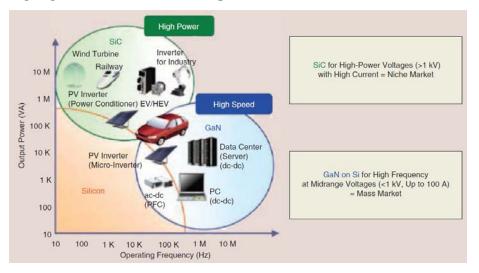

| Figure 1.5. Classification of power devices according to their rated power and<br>switching frequency, and their applications. Source: Yole Développement web 8                                                                                           |

| Figure 1.6. Perspective on WBG technologies in terms of frequency and power.<br>Source: [6]                                                                                                                                                               |

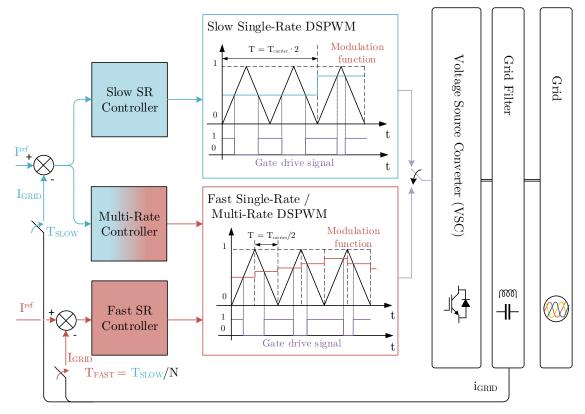

| FIGURE 1.7. SIMPLIFIED BLOCK DIAGRAM OF SINGLE-RATE AND MULTIRATE EXAMPLE OF<br>CURRENT-CONTROLLED SYSTEMS                                                                                                                                                |

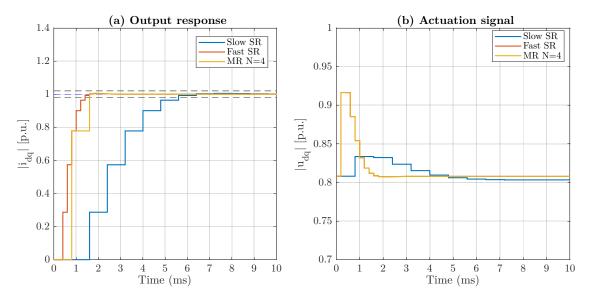

| Figure 1.8. Comparison of slow and fast single-rate responses with the multirate Approach of a current-controlled system                                                                                                                                  |

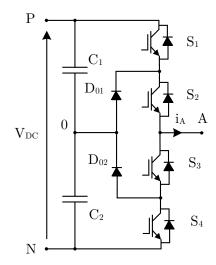

| FIGURE 1.9. PHASE STRUCTURE OF A 3L DNPC VSC 12                                                                                                                                                                                                           |

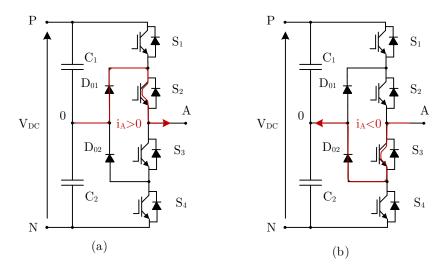

| FIGURE 1.10. PHASE CURRENT PATH IN 3L-DNP-VSC: (A)POSITIVE (OUTGOING); (B)NEGATIVE (INCOMING)                                                                                                                                                             |

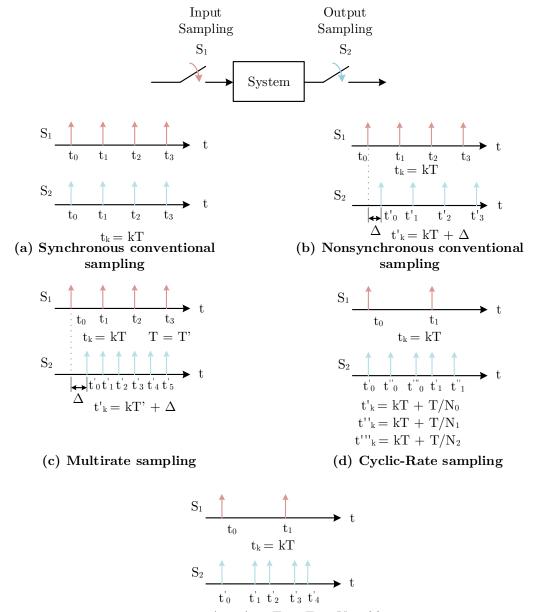

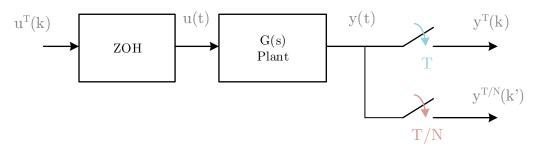

| FIGURE 2.1. SCHEMATICS OF SAMPLING PROCESSES 17                                                                                                                                                                                                           |

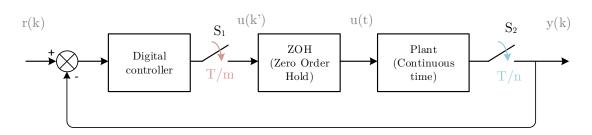

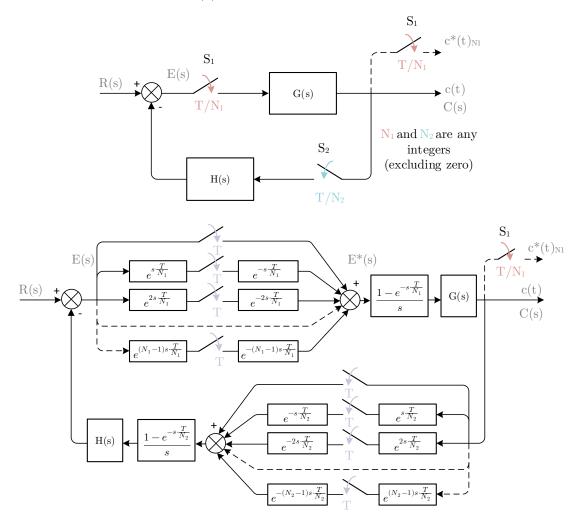

| FIGURE 2.2. SISO STRUCTURE WITH NON-CONVENTIONAL SAMPLING                                                                                                                                                                                                 |

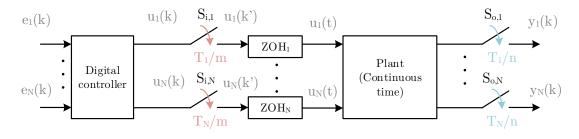

| FIGURE 2.3. MIMO STRUCTURE WITH NON-CONVENTIONAL SAMPLING                                                                                                                                                                                                 |

| FIGURE 2.4. FREQUENCY DECOMPOSITION SCHEME                                                                                                                                                                                                                |

| Figure 2.5. Vectorial Switch Decomposition of a control system with multirate sampling                                                                                                                                                                    |

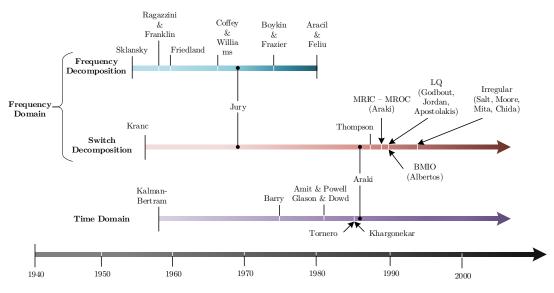

| FIGURE 2.6. HISTORICAL BACKGROUND                                                                                                                                                                                                                         |

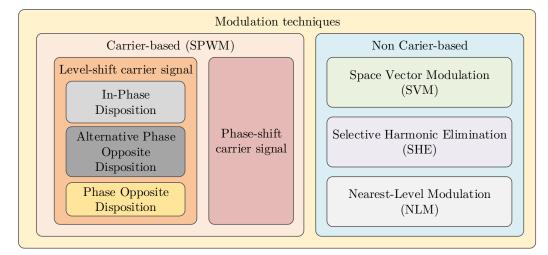

| FIGURE 2.7. MAIN MODULATION TECHNIQUES IN POWER CONVERTERS                                                                                                                                                                                                |

| Figure 2.8. SPWM example with $ma=0.85$ and $mf=15$                                                                                                                                                                                                       |

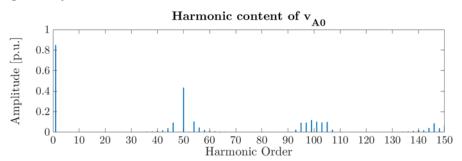

| FIGURE 2.9. HARMONIC CONTENT OF PHASE-TO-NEUTRAL VOLTAGE FOR $ma = 0.85$ and $mf = 50$ with IPD carrier signals                                                                                                                                           |

| FIGURE 2.10. HARMONIC CONTENT OF PHASE-TO-NEUTRAL VOLTAGE FOR $ma = 0.85$ and $mf = 50$ with POD carrier signals                                                                                                                                          |

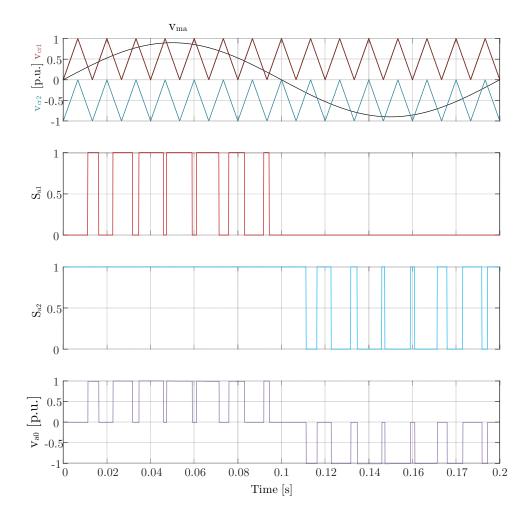

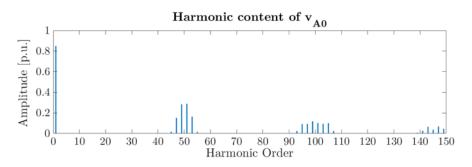

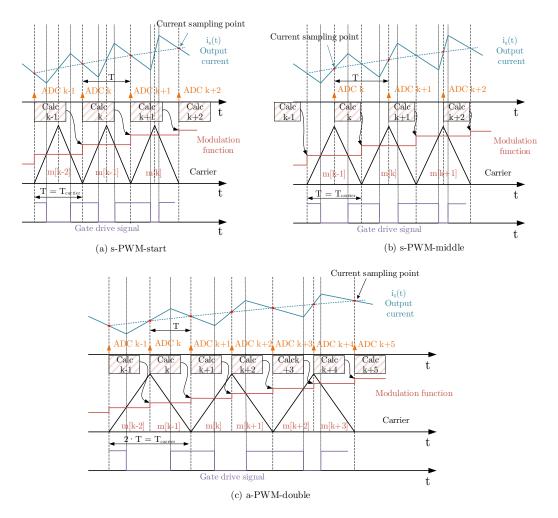

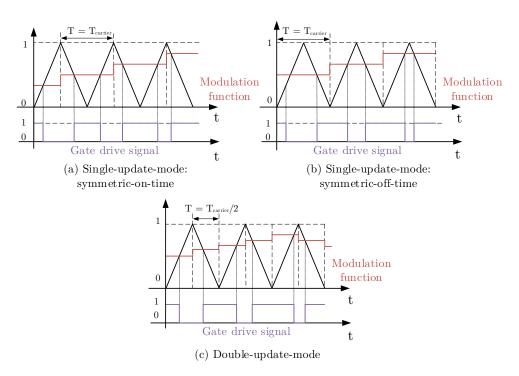

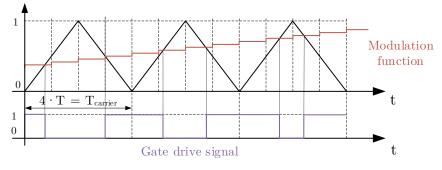

| Figure 2.11. Schematic of Regular sampled PWM strategies with equivalent carrier<br>signal: (a) Symmetrical PWM with sampling at start; (b) Symmetrical PWM with<br>regular sampling at middle; (c) Asymmetrical PWM with sampling at start and<br>middle |

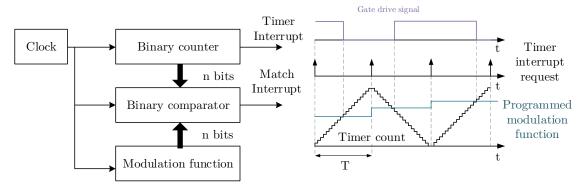

| Figure 2.12. Simplified structure of a digital SPWM                                                                                                                                                                                                       |

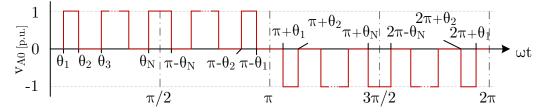

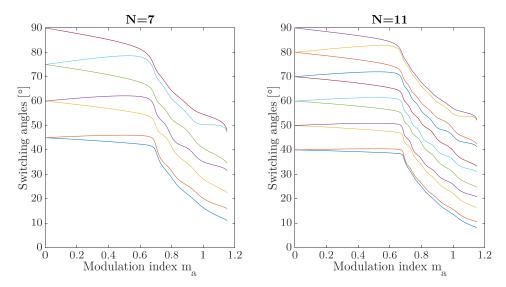

| FIGURE 2.13. GENERIC THREE-LEVEL WAVEFORM WITH QUARTER-WAVE SYMMETRY                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.14. Switching angles versus amplitude modulation index for a three-phase<br>three-level converter when N is 7 and 11                                                                                            |

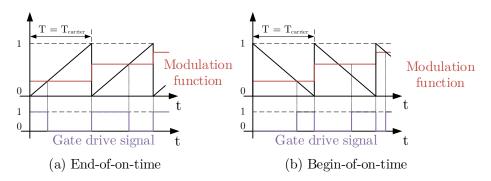

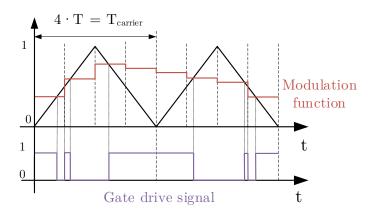

| FIGURE 2.15. SAWTOOTH CARRIER MODULATORS                                                                                                                                                                                 |

| FIGURE 2.16. TRIANGULAR CARRIER MODULATORS                                                                                                                                                                               |

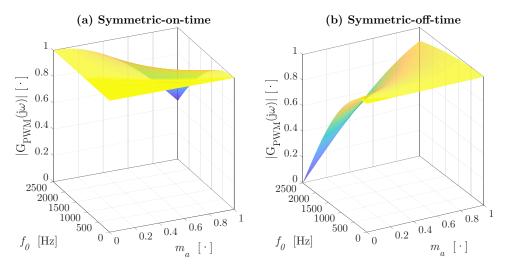

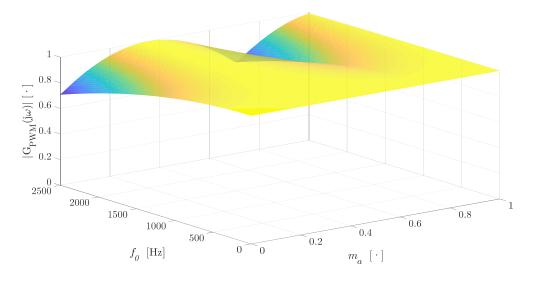

| FIGURE 2.17. DEPENDENCE OF THE SINGLE-UPDATE-MODE GAIN REGARDING MODULATING<br>FREQUENCY $f0$ and amplitude modulation index $ma$ , being $T = 200 \ \mu s$ and<br>$Tcarrier = 200 \ \mu s$                              |

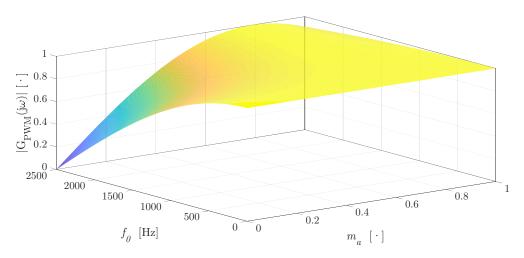

| FIGURE 2.18. DEPENDENCE OF THE DOUBLE-UPDATE-MODE GAIN REGARDING MODULATING<br>FREQUENCY $f0$ and amplitude modulation index $ma$ , being $T = 200 \ \mu s$ and<br>$Tcarrier = 400 \ \mu s$                              |

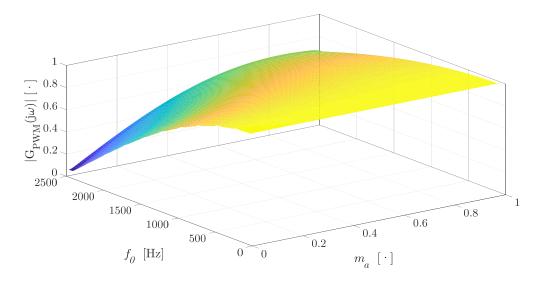

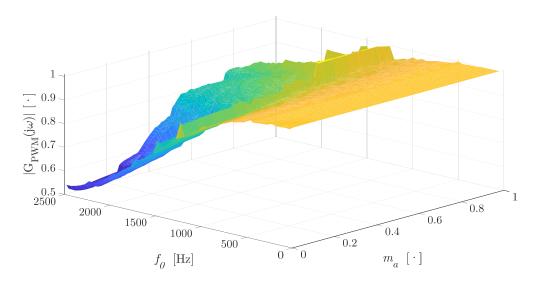

| FIGURE 2.19. PARAMETRIC DSPWM SIMULATION OF DOUBLE-UPDATE-MODE GAIN REGARDING<br>MODULATING FREQUENCY $f0$ and Amplitude Modulation index $ma$ , being $T = 200 \ \mu s$<br>AND $Tcarrier = 400 \ \mu s$                 |

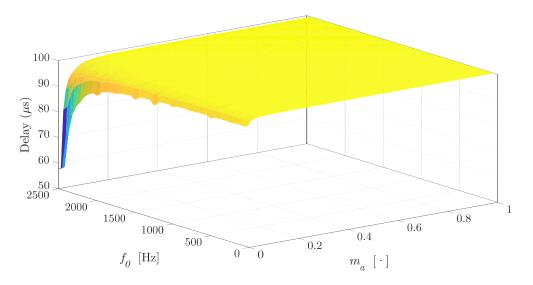

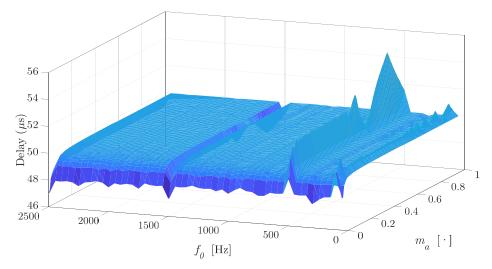

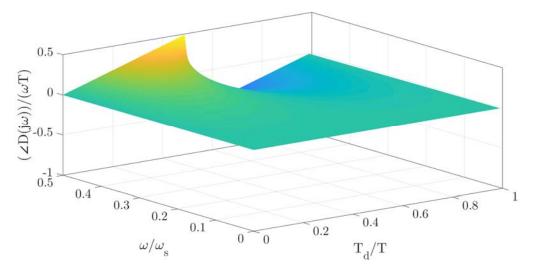

| FIGURE 2.20. PARAMETRIC DSPWM SIMULATION OF DOUBLE-UPDATE MODE DELAY REGARDING<br>MODULATING FREQUENCY $f0$ and AMPLITUDE MODULATION INDEX $ma$ , BEING $T = 200 \ \mu s$<br>AND $Tcarrier = 400 \ \mu s$                |

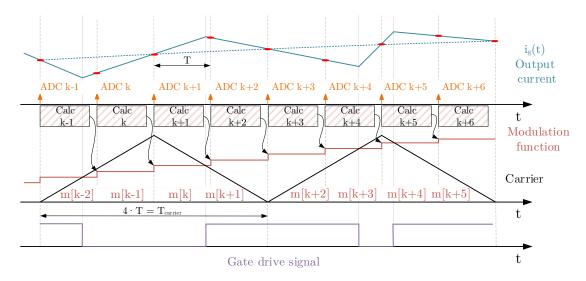

| Figure 2.21. Multi-sampled PWM                                                                                                                                                                                           |

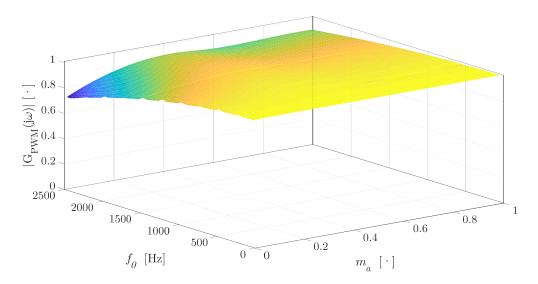

| FIGURE 2.22. Multi-sampled $(N = 4)$ mode gain regarding modulating frequency $f0$<br>and amplitude modulation index $ma$ , being $T = 100 \ \mu s$ and $Tcarrier = 400 \ \mu s$ 36                                      |

| FIGURE 2.23. PARAMETRIC DSPWM SIMULATION OF MULTI-SAMPLED ( $N = 4$ ) MODE GAIN<br>REGARDING MODULATING FREQUENCY $f0$ and AMPLITUDE MODULATION INDEX $ma$ , BEING<br>$T = 100 \ \mu s$ and $Tcarrier = 400 \ \mu s$     |

| FIGURE 2.24. PARAMETRIC DSPWM SIMULATION OF MULTI-SAMPLED $(N = 4)$ mode delay<br>TIME REGARDING MODULATING FREQUENCY $f0$ and AMPLITUDE MODULATION INDEX $ma$ ,<br>BEING $T = 100 \ \mu s$ and $Tcarrier = 400 \ \mu s$ |

| FIGURE 2.25. MULTI-SAMPLED PWM STRATEGY WITH SAMPLING OF CURRENT NOISE                                                                                                                                                   |

|                                                                                                                                                                                                                          |

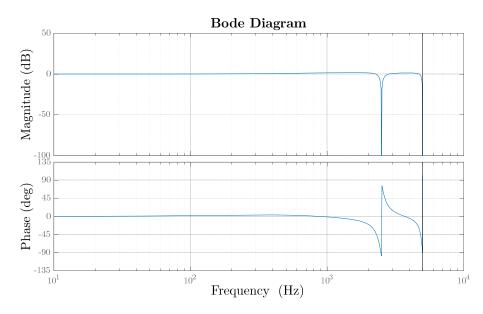

| FIGURE 2.26. BODE DIAGRAM OF $F(z)$ with $Tcarrier = 400 \ \mu s$ and $N = 4$                                                                                                                                            |

| FIGURE 2.26. BODE DIAGRAM OF $F(z)$ WITH $Tcarrier = 400 \ \mu s$ and $N = 4$                                                                                                                                            |

|                                                                                                                                                                                                                          |

| FIGURE 2.27. MULTI-SAMPLED PWM WITH MULTIPLE CROSSING PER HALF CARRIER PERIOD 39                                                                                                                                         |

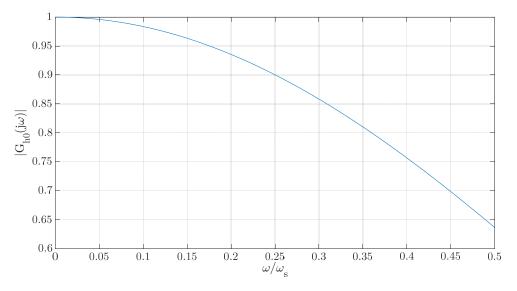

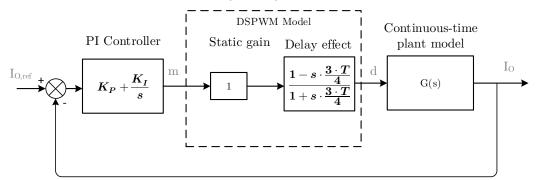

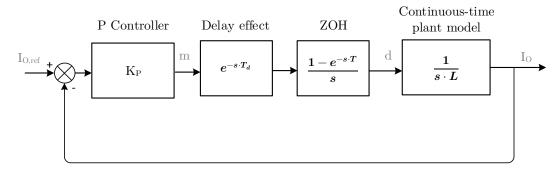

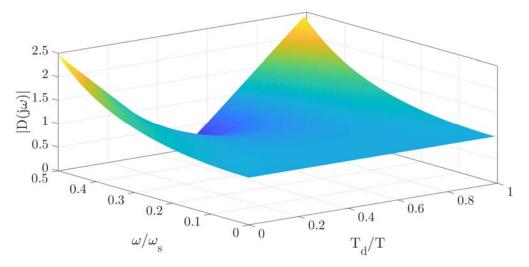

| FIGURE 2.27. MULTI-SAMPLED PWM WITH MULTIPLE CROSSING PER HALF CARRIER PERIOD 39<br>FIGURE 2.28. FREQUENCY RESPONSE OF THE ZOH OPERATION                                                                                 |

| FIGURE 2.27. MULTI-SAMPLED PWM WITH MULTIPLE CROSSING PER HALF CARRIER PERIOD                                                                                                                                            |

| FIGURE 2.27. MULTI-SAMPLED PWM WITH MULTIPLE CROSSING PER HALF CARRIER PERIOD                                                                                                                                            |

| Figure 2.34. Sampling of current shifted towards the modulating signal update $\dots$ 46                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 2.35. MULTIRATE ZERO-CROSSING SAMPLING DIGITAL PLL                                                                                                                                                                                                                                                                                       |

| FIGURE 2.36. BLOCK DIAGRAM OF THE MULTIRATE PLL                                                                                                                                                                                                                                                                                                 |

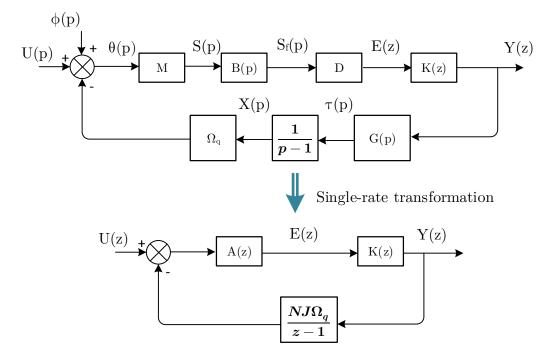

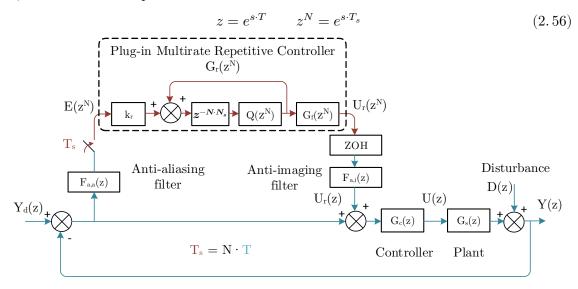

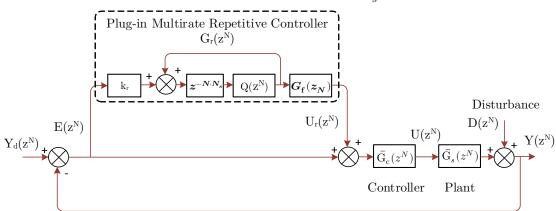

| FIGURE 2.37. MULTIRATE RC SYSTEM                                                                                                                                                                                                                                                                                                                |

| FIGURE 2.38. EQUIVALENT SINGLE-RATE RC                                                                                                                                                                                                                                                                                                          |

| FIGURE 2.39. COMPACT REPRESENTATION OF A MULTIRATE SYSTEM                                                                                                                                                                                                                                                                                       |

| FIGURE 2.40. SINGLE-RATE EQUIVALENT SYSTEM                                                                                                                                                                                                                                                                                                      |

| FIGURE 2.41. GRAPHICAL REPRESENTATION OF THE PARAMETERS FOR INTERNAL REPRESENTATION                                                                                                                                                                                                                                                             |

| FIGURE 2.42. ANALYZED REGULAR CASE FOR EXTERNAL REPRESENTATION MODELLING                                                                                                                                                                                                                                                                        |

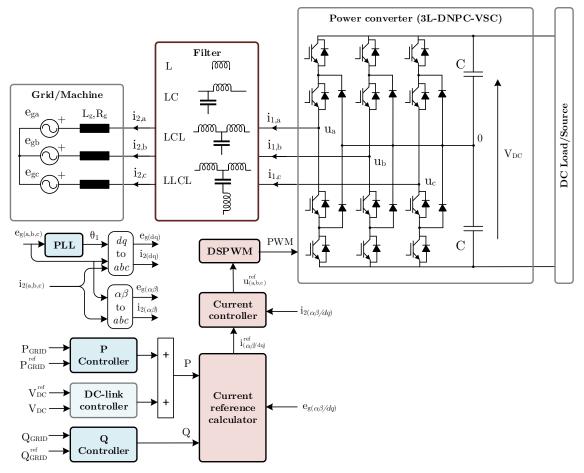

| FIGURE 3.1. SCHEMATIC BLOCK DIAGRAM OF THE SYSTEM UNDER STUDY                                                                                                                                                                                                                                                                                   |

| FIGURE 3.2. Schematic circuit of an L-filter                                                                                                                                                                                                                                                                                                    |

| FIGURE 3.3. SCHEMATIC CIRCUIT OF AN LC-FILTER                                                                                                                                                                                                                                                                                                   |

| FIGURE 3.4. Schematic circuit of an LCL-filter                                                                                                                                                                                                                                                                                                  |

| FIGURE 3.5. BLOCK DIAGRAM OF PHASE DELAY COMPENSATION IN STATIONARY REFERENCE FRAME                                                                                                                                                                                                                                                             |

| FIGURE 3.6. BLOCK DIAGRAM OF PHASE DELAY COMPENSATION IN ROTATING REFERENCE FRAME                                                                                                                                                                                                                                                               |

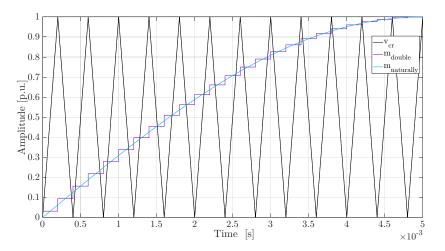

| FIGURE 3.7. REGULAR SAMPLING WITH PHASE ADVANCED MODULATING SIGNAL (DOUBLE-UPDATE MODE). PARAMETERS: $fSW = 2.5 \ kHz$ , $f1 = 50 \ Hz$ , $T = 200 \ \mu s$ , $ma = 1$                                                                                                                                                                          |

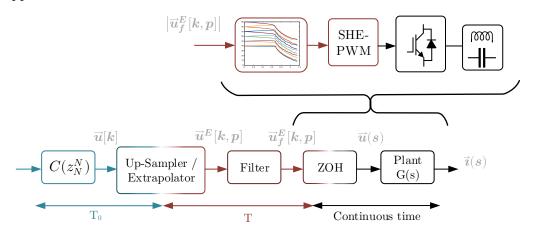

| Figure 3.8. Proposed extrapolation method for DSPWM for $N = 2$ (double-update mode)                                                                                                                                                                                                                                                            |

| FIGURE 3.9. BLOCK DIAGRAM OF THE CURRENT CONTROL LOOP WITH EXTRAPOLATION OF MODULATING SIGNAL                                                                                                                                                                                                                                                   |

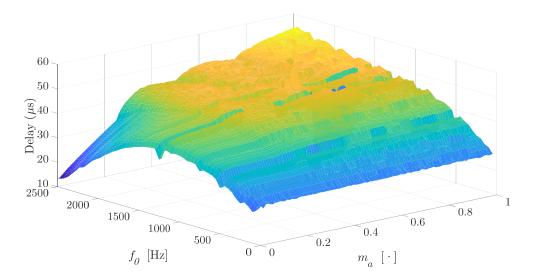

| FIGURE 3.10. PARAMETRIC DSPWM SIMULATION OF EXTRAPOLATED MODULATING SIGNAL REGARDING MODULATING FREQUENCY $f0$ and AMPLITUDE MODULATION INDEX $ma$ .<br>PARAMETERS: $fSW = 2.5 \ kHz$ , $f1 = 50 \ Hz$ , $T0 = 200 \ \mu s$ , $N = 4$                                                                                                           |

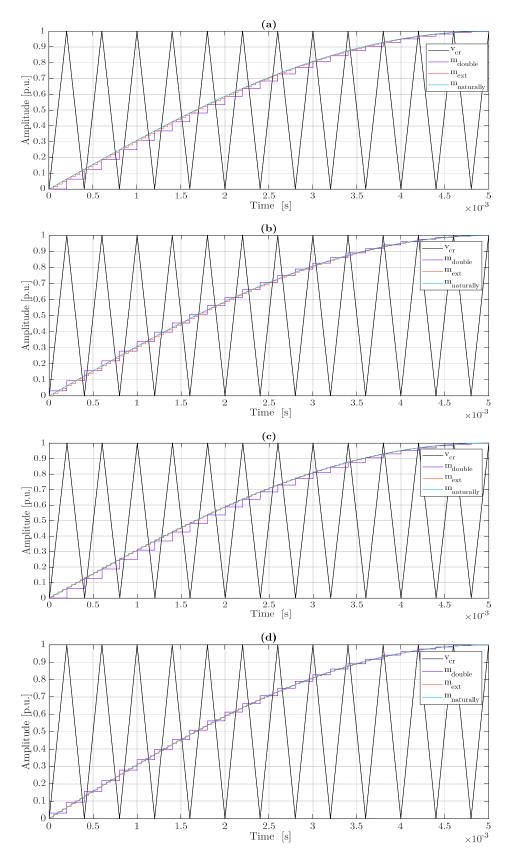

| FIGURE 3.11. CARRIER CROSSING COMPARISON OF MODULATING SIGNALS: (A) NON-ADVANCED<br>mext and NON-ADVANCED mdouble; (B) NON-ADVANCED mext and ADVANCED<br>mdouble; (C) ADVANCED mext and NON-ADVANCED mdouble; (D) ADVANCED mext<br>AND ADVANCED mdouble. PARAMETERS: $fSW = 2.5 \ kHz$ , $f1 = 50 \ Hz$ , $T0 = 200 \ \mu s$ ,<br>ma = 1, N = 4 |

| FIGURE 3.12. PARAMETRIC DSPWM SIMULATION OF EXTRAPOLATED MODULATING SIGNAL REGARDING MODULATING FREQUENCY $f0$ and AMPLITUDE MODULATION INDEX $ma$ .<br>PARAMETERS: $fSW = 2.5 \ kHz$ , $f1 = 50 \ Hz$ , $T0 = 200 \ \mu s$ , $N = 4$                                                                                                           |

| FIGURE 3.13. BLOCK DIAGRAM OF THE PROPOSED OPEN LOOP CONTROLLER FOR SHE                                                                                                                                                                                                                                                                         |

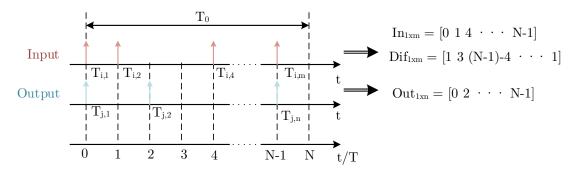

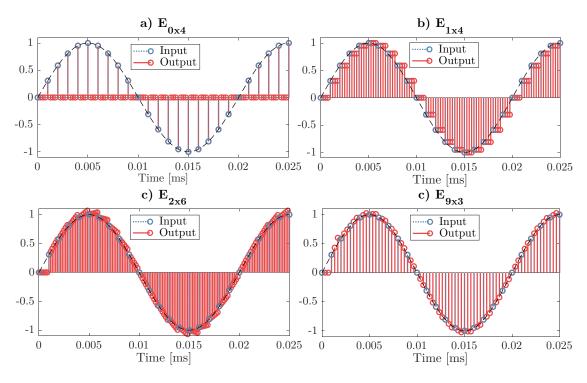

| FIGURE 3.14. TIME DOMAIN CHARACTERIZATION OF UP-SAMPLING. PARAMETERS: $f1 = 50 Hz$ ,<br>T0 = 1 ms                                                                                                                                                                                                                                               |

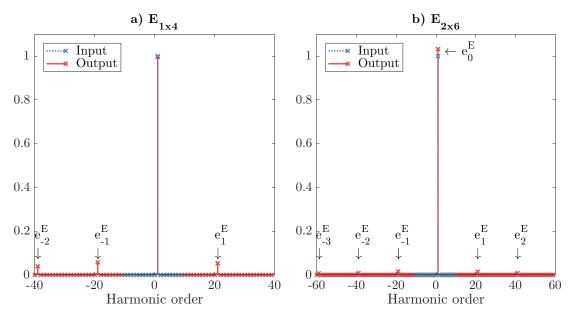

| FIGURE 3.15. FREQUENCY SPECTRUM OF VECTORS. PARAMETERS: $f1 = 50 Hz$ , $T0 = 1 ms$ 84                                                                                                                                                                                                                                                           |

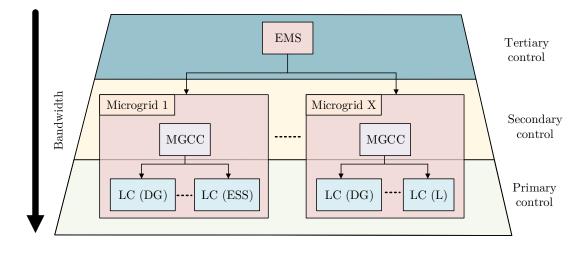

| FIGURE 3.16. REGULATION PYRAMID OF MG                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

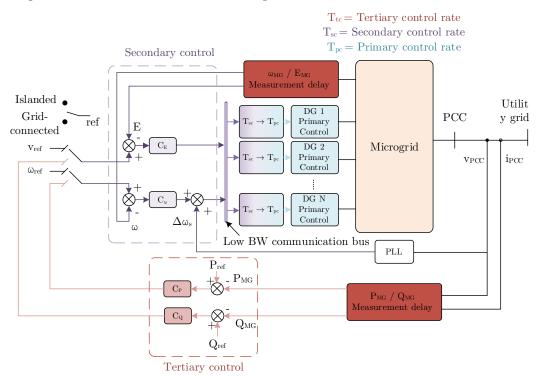

| FIGURE 3.17. CONTROL STRUCTURE OF SECONDARY AND TERTIARY CONTROL LEVELS                                                                                          |

| FIGURE 3.18. HIERARCHICAL CONTROL WITH DIFFERENT RATES PER CONTROL LEVEL                                                                                         |

| FIGURE 4.1. SIMPLIFIED BLOCK DIAGRAM OF THE CONTROLLED SYSTEM                                                                                                    |

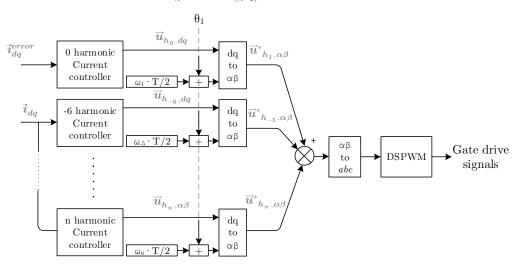

| FIGURE 4.2. BLOCK DIAGRAM OF ROGI-BASED CURRENT CONTROL SYSTEM                                                                                                   |

| FIGURE 4.3. POLE-ZERO MAP OF ROGI-CONTROLLED CLOSED-LOOP TRANSFER FUNCTION                                                                                       |

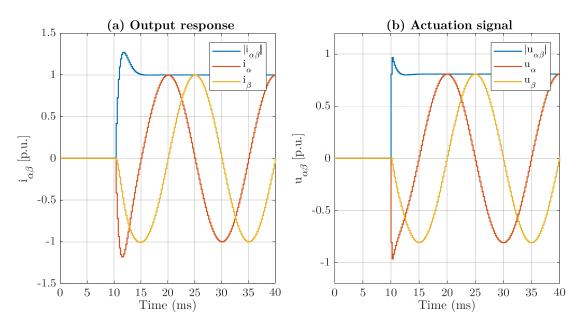

| FIGURE 4.4. TIME RESPONSE OF ROGI-BASED CURRENT CONTROL SYSTEM. (A) OUTPUT<br>CURRENT; (B) VSC VOLTAGE                                                           |

| FIGURE 4.5. BLOCK DIAGRAM OF DQ-FRAME COMPLEX-VALUED CURRENT CONTROL SYSTEM 97                                                                                   |

| FIGURE 4.6. POLE-ZERO MAP OF OPEN AND CLOSED-LOOP TRANSFER FUNCTIONS IN DQ-FRAME 97                                                                              |

| FIGURE 4.7. TIME RESPONSE OF COMPLEX-VALUED DQ-FRAME CURRENT CONTROL SYSTEM. (A)<br>OUTPUT CURRENT; (B) VSC VOLTAGE                                              |

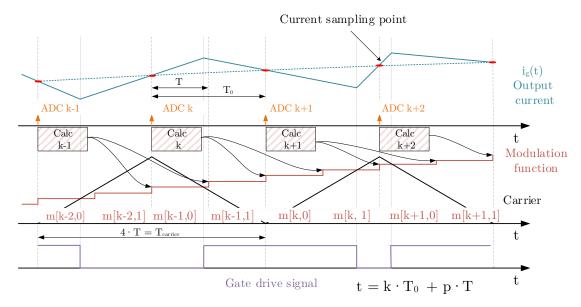

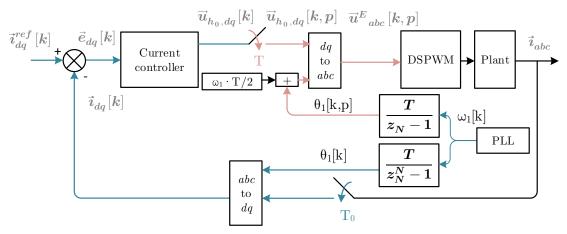

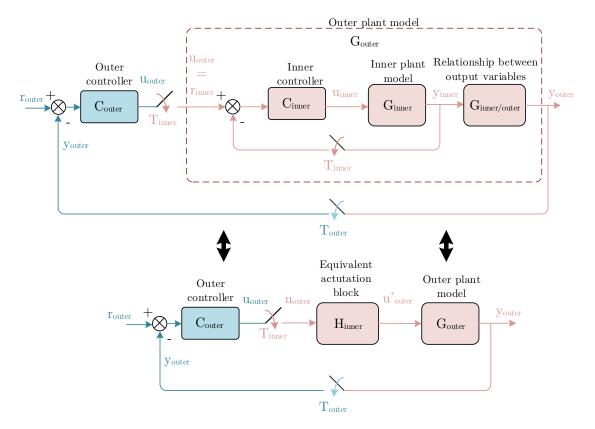

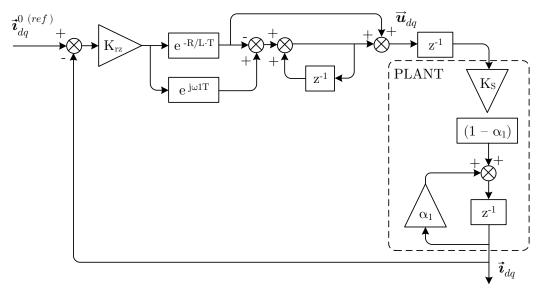

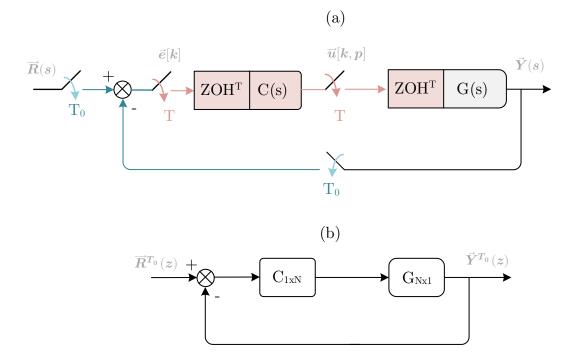

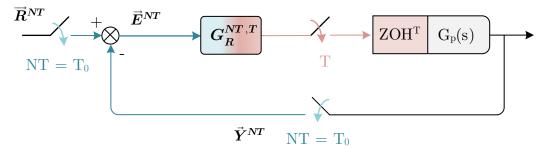

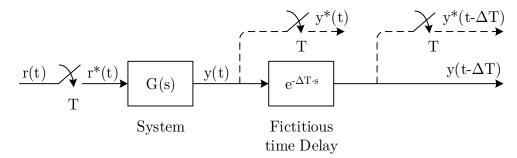

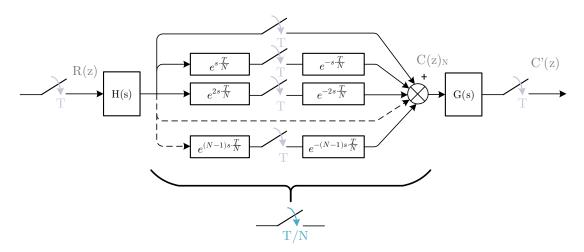

| Figure 4.8. Block diagram of proposed multirate system. (a)Distribution of signals on the closed-loop; (b) Equivalent discrete closed loop at metaperiod $T0$ 99 |

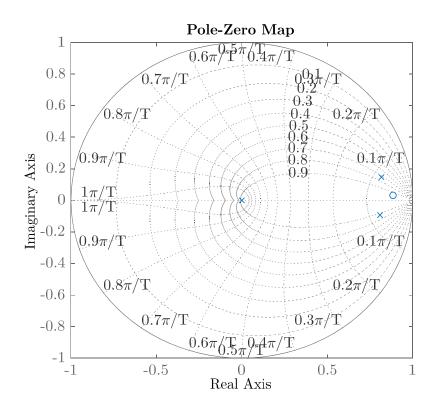

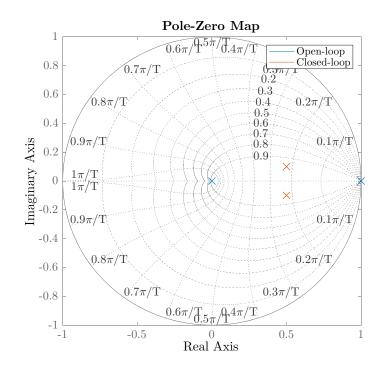

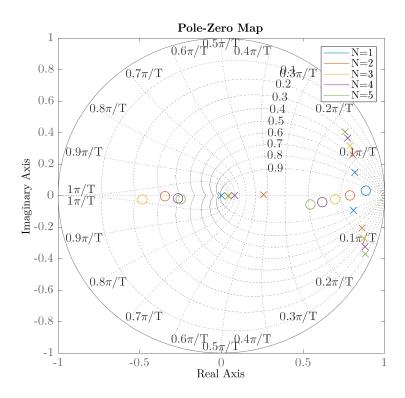

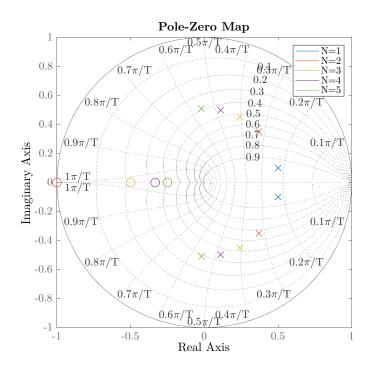

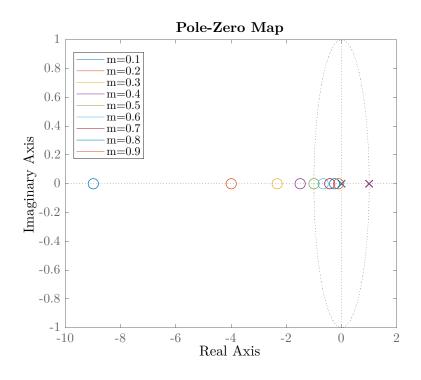

| Figure 4.9. Pole-zero map of $\alpha\beta$ -frame closed-loop transfer function at $T0=200 \ \mu s$ .                                                            |

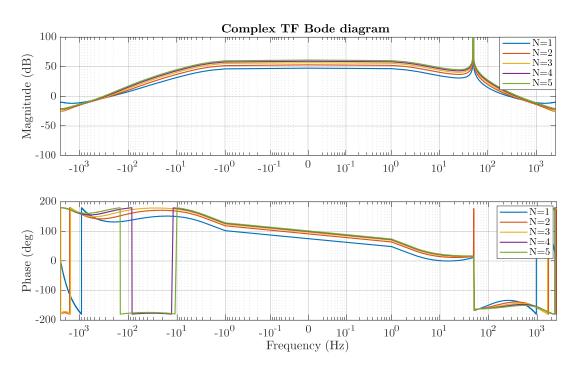

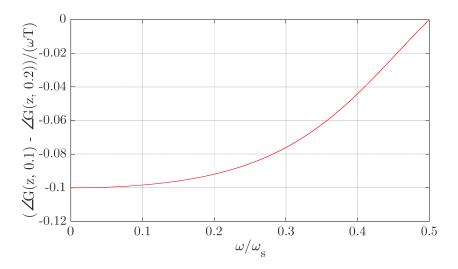

| Figure 4.10. Bode diagram of $\alpha\beta$ -frame complex-valued open-loop transfer function<br>at $T0 = 200 \ \mu s$                                            |

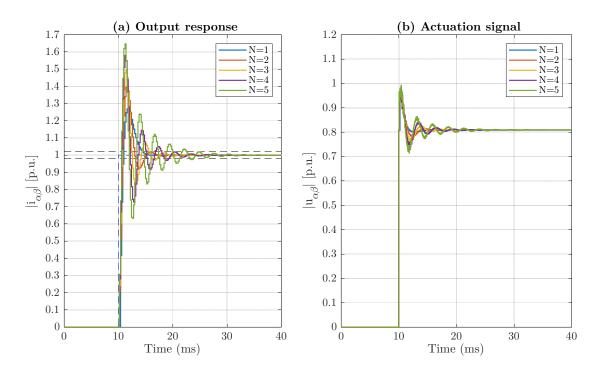

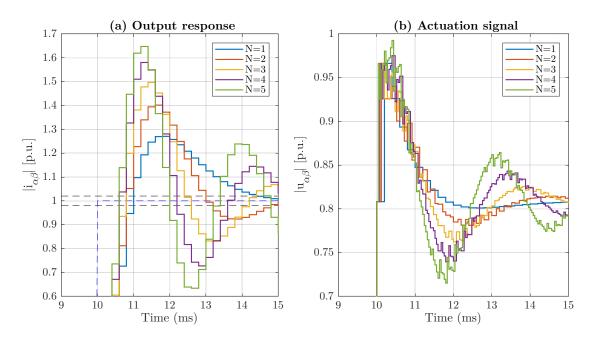

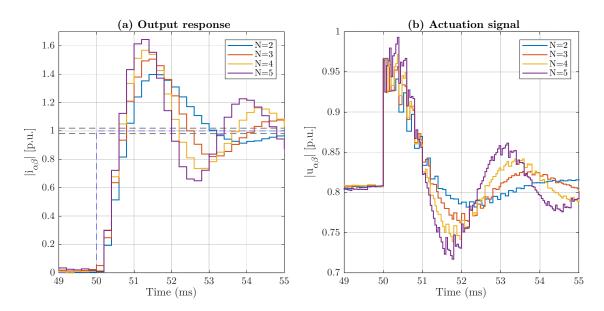

| Figure 4.11. Time response of complex-valued $\alpha\beta$ -frame current control system: (a)<br>Output current; (b) VSC voltage                                 |

| Figure 4.12. Zoom on time response of complex-valued $\alpha\beta$ -frame current control system: (a) Output current; (b) VSC voltage                            |

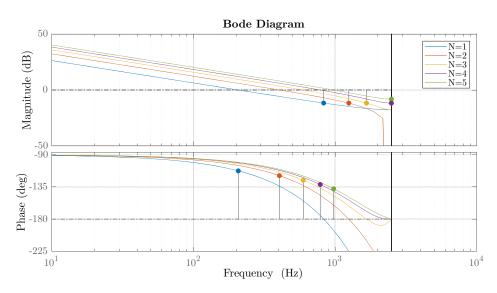

| Figure 4.13. P Pole-zero map of dQ-frame closed-loop transfer function at $T0 = 200 \ \mu s$                                                                     |

| Figure 4.14. Bode diagram of dQ-frame open-loop transfer function at $T0=200 \ \mu s$                                                                            |

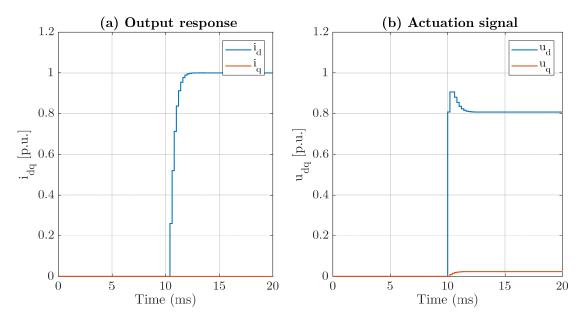

| FIGURE 4.15. TIME RESPONSE OF DQ-FRAME CURRENT CONTROL SYSTEM: (A) OUTPUT CURRENT;<br>(B) VSC VOLTAGE                                                            |

| Figure 4.16. Time response of detailed system in $\alpha\beta$ -frame: (a) Output current; (b)<br>VSC voltage                                                    |

| Figure 4.17. Time response of detailed system in <b><i>dq</i></b> -frame: (A) Output current; (B) VSC voltage                                                    |

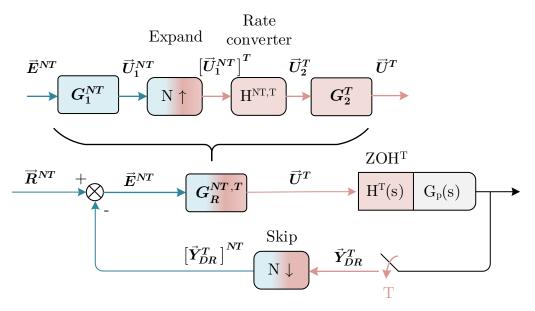

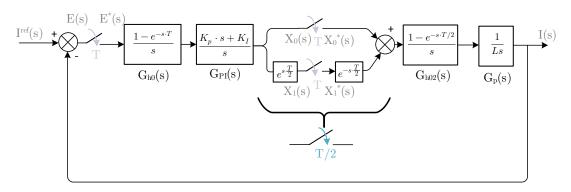

| FIGURE 4.18. BLOCK DIAGRAM OF MODEL-BASED MULTIRATE CONTROL APPROACH107                                                                                          |

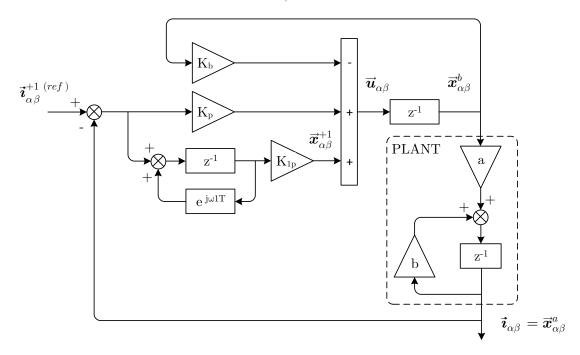

| FIGURE 4.19. BLOCK DIAGRAM OF THE MRIC110                                                                                                                        |

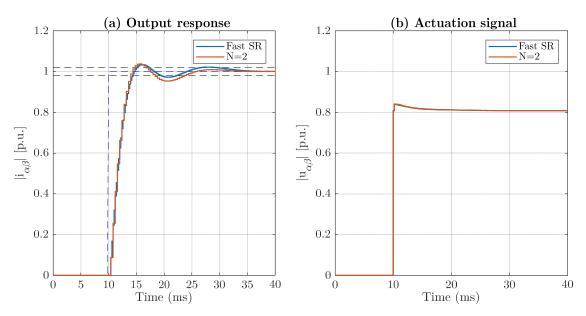

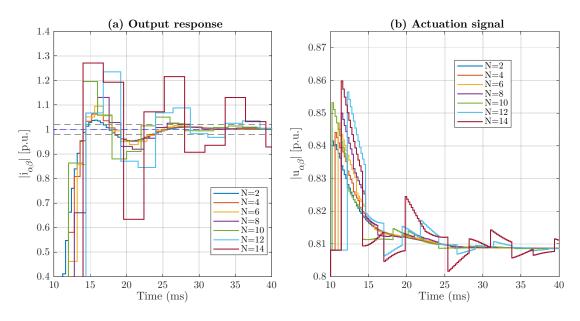

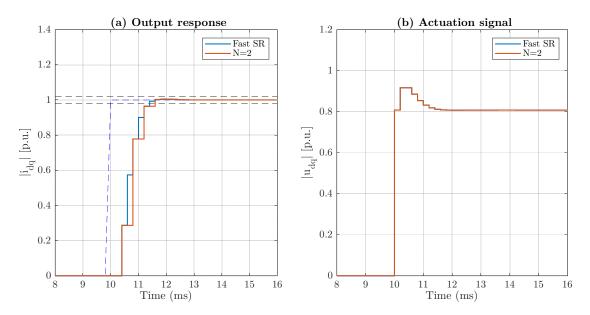

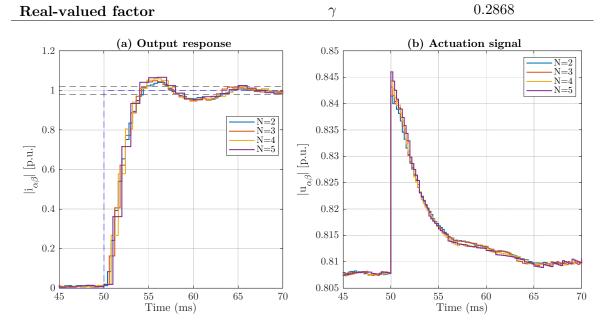

| Figure 4.20. MRIC response (N=2) compared to the single-rate (SR) fast controlled system for $\alpha\beta$ -frame                                                |

| Figure 4.21. Detailed MRIC response (N=2) compared to the single-rate (SR) fast controlled system for $\alpha\beta$ -frame                                       |

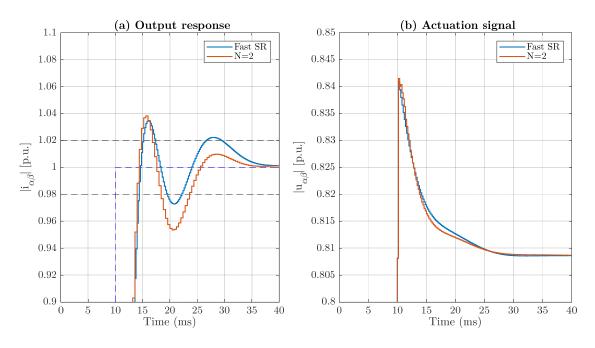

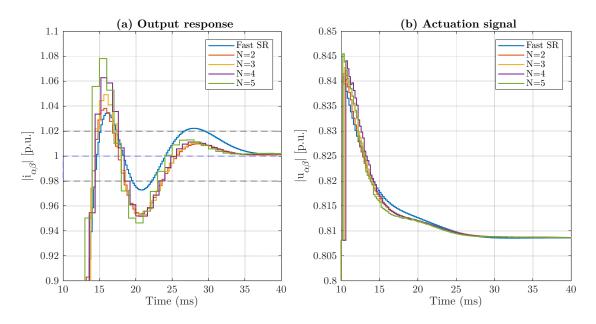

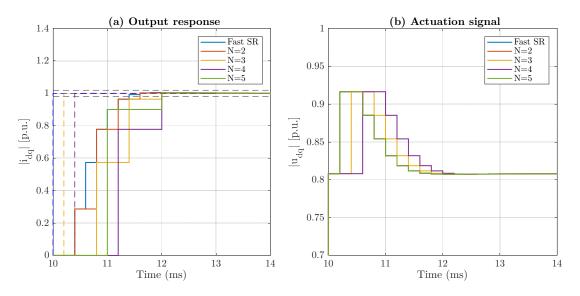

| Figure 4.22. MRIC response with different values of N compared to the single-rate fast controlled system for $\alpha\beta$ -frame |

|-----------------------------------------------------------------------------------------------------------------------------------|

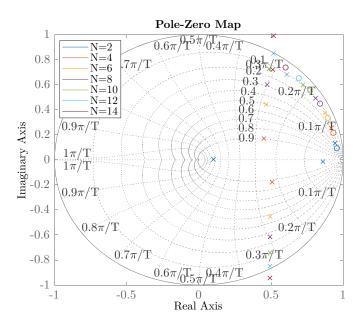

| Figure 4.23. Pole-zero map of $MRNTzN$ for $\alpha\beta$ -frame                                                                   |

| Figure 4.24. MRIC response with high N values for $lphaeta$ -frame                                                                |

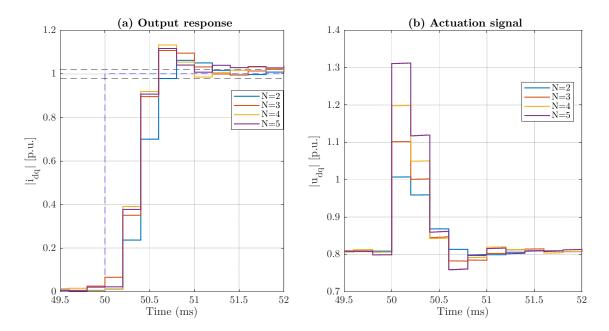

| Figure 4.25. MRIC response (N=2) compared to the single-rate (SR) fast controlled system for $dq$ -frame                          |

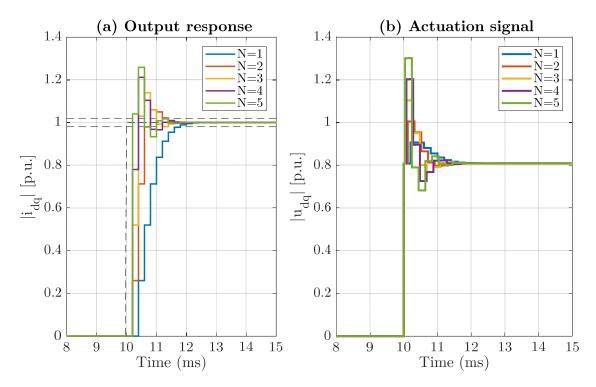

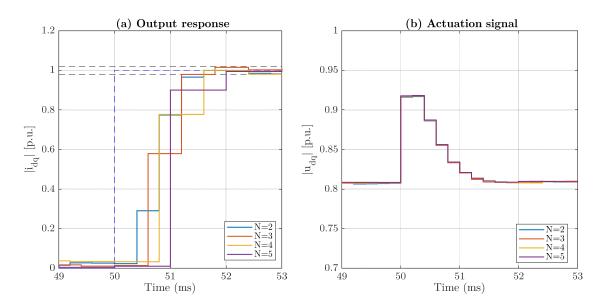

| FIGURE 4.26. MRIC RESPONSE WITH DIFFERENT VALUES OF N FOR DQ-FRAME118                                                             |

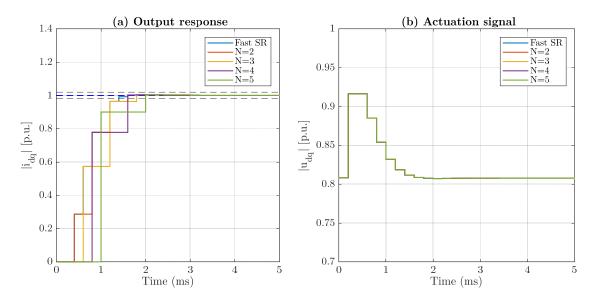

| Figure 4.27. MRIC controlled <b>dq</b> -frame system response with different values of N and step instant placed in 0 ms          |

| FIGURE 4.28. COMPARISON OF SLOW SINGLE-RATE (SR) RESPONSE TO THE ONE WITH MRIC CONTROLLED <b>dq</b> -FRAME SYSTEM                 |

| FIGURE 4.29. TIME RESPONSE OF DETAILED MRIC SYSTEM IN $\alpha\beta$ -FRAME: (A) OUTPUT CURRENT;<br>(B) VSC VOLTAGE                |

| FIGURE 4.30. TIME RESPONSE OF DETAILED MRIC SYSTEM IN <b><i>dq</i></b> -FRAME: (A) OUTPUT CURRENT;<br>(B) VSC VOLTAGE             |

### LIST OF TABLES

| TABLE 1.1. VOLTAGE RANGES. SOURCE: IEC 60038                                                            |

|---------------------------------------------------------------------------------------------------------|

| TABLE 1.2. MARKET OVERVIEW OF INDUSTRIAL 3L-NPC-VSC MV DRIVES. SOURCE:       [2]                        |

| TABLE 1.3. SWITCHING STATES ON THE 3L DNPC VSC 12                                                       |

| TABLE 2.1. SWITCHING RULE ON A 3L-DNPC-VSC.    23                                                       |

| TABLE 2.2. THE FREQUENCY AND LAPLACE DOMAIN MODELS FOR REGULAR SAMPLED PWM.         SOURCE:[52]         |

| TABLE 2.3. GRID-TIED CONVERTER WITH L-FILTER TRANSFER FUNCTIONS FOR EACH STRATEGY.         SOURCE: [48] |

| TABLE 4.1. 3L-DNPC-VSC PARAMETERS                                                                       |

| TABLE 4.2. VSC parameters for multirate time-domain analysis in detailed model $\dots 105$              |

| TABLE 4.3. CONTROLLERS PARAMETERS FOR MULTIRATE TIME-DOMAIN ANALYSIS IN DETAILED         MODEL          |

| TABLE 4.4. SRF-PLL PARAMETERS                                                                           |

| TABLE 4.5. VSC parameters for multirate time-domain analysis in detailed model $\dots 120$              |

| TABLE 4.6. SRF-PLL PARAMETERS                                                                           |

| TABLE 4.7. CONTROLLERS PARAMETERS FOR MULTIRATE TIME-DOMAIN ANALYSIS IN DETAILED      MODEL             |

| TABLE 5.1. MULTIRATE APPLICATION IDENTIFICATION IN POWER ELECTRONICS       129                          |

| TABLE 6.1. MATERIAL COSTS (VAT INCLUDED)                                                                |

| TABLE 6.2. PROFESSIONAL FEES (GROSS SALARY)    131                                                      |

| TABLE 6.3. ADDITIONAL COSTS AND TOTAL    131                                                            |

## LIST OF ACRONYMS

| AC                   | Alternating Current                                         |  |  |

|----------------------|-------------------------------------------------------------|--|--|

| ADC                  | Alternating Current                                         |  |  |

| ADC                  | Analog-to-Digital Converter<br>Active Neutral Point Clamped |  |  |

| APF                  | Active Power Filter                                         |  |  |

| APOD                 |                                                             |  |  |

| BJT                  | Alternate Phase Opposite Disposition                        |  |  |

|                      | Bipolar Junction Transistor                                 |  |  |

| BMIO                 | Block Multirate Input Output                                |  |  |

| CSC                  | Current-Source Converter                                    |  |  |

| DBS                  | Distributed Bus Signaling                                   |  |  |

| DC                   | Direct Current                                              |  |  |

| DG                   | Distributed Generator                                       |  |  |

| DNPC                 | Diode Neutral Point Clamped                                 |  |  |

| DSP                  | Digital Signal Processor                                    |  |  |

| DSPWM                | Digital Sinusoidal Pulse Width Modulation                   |  |  |

| $\operatorname{EES}$ | Energy Storage System                                       |  |  |

| $\operatorname{EMF}$ | Electromotive Force                                         |  |  |

| $\mathbf{EMS}$       | Energy Management System                                    |  |  |

| $\mathbf{ER}$        | External Representation                                     |  |  |

| $\mathrm{EU}$        | European Union                                              |  |  |

| FACTS                | Flexible AC Transmission Systems                            |  |  |

| FPGA                 | Field-Programmable Gate Array                               |  |  |

| GCD                  | Greatest Common Divisor                                     |  |  |

| GTO                  | Gate Turn-Off Thyristors                                    |  |  |

| IGCT                 | Integrated Gate-Commutated Thyristors                       |  |  |

| IGBT                 | Insulated Gate Bipolar Transistor                           |  |  |

| IPD                  | In-Phase Disposition                                        |  |  |

| IR                   | Internal Representation                                     |  |  |

| LC                   | Local Controller                                            |  |  |

| LQR                  | Linear Quadratic Regulator                                  |  |  |

| LTI                  | Linear Time-Invariant                                       |  |  |

| LV                   | Low Voltage                                                 |  |  |

| MAS                  | Multi-Agent System                                          |  |  |

| MIMO                 | Multiple-Input Multiple-Output                              |  |  |

| MG                   | MicroGrid                                                   |  |  |

| MGCC                 | MicroGrid Central Controller                                |  |  |

| MOSFET               | Metal-Oxide-Semiconductor Field-Effect Transistor           |  |  |

| MRFORC               | Multi-Rate Fractional-Order Repetitive Control              |  |  |

| MRIC                 | Multi-Rate Input Controller                                 |  |  |

| MROC                 | Multi-Rate Output Controller                                |  |  |

|                      |                                                             |  |  |

| MV            | Medium Voltage                                   |  |  |  |

|---------------|--------------------------------------------------|--|--|--|

| NCO           | Numerically Controller Oscillator                |  |  |  |

| NLM           | Nearest Level Modulation                         |  |  |  |

| NPC           | Neutral Point Clamped                            |  |  |  |

| PI            | Proportional Integral                            |  |  |  |

| PLC           | Power Line Communication                         |  |  |  |

| PLL           | Phase-Locked Loop                                |  |  |  |

| POD           | Phase Opposite Disposition                       |  |  |  |

| PVT           | Periodically Variable in Time                    |  |  |  |

| PWM           | Pulse Width Modulation                           |  |  |  |

| $\mathbf{RC}$ | Repetitive Control                               |  |  |  |

| ROGI          | Reduced Order Generalized Integrator             |  |  |  |

| SCR           | Silicon Controlled Rectifier                     |  |  |  |

| SISO          | Single-Input Single-Output                       |  |  |  |

| SHE           | Selective-Harmonic Elimination                   |  |  |  |

| SPWM          | Sinusoidal Pulse Width Modulation                |  |  |  |

| SRF-PLL       | Synchronous Reference Frame Phase-Locked Loop    |  |  |  |

| STATCOM       | Static synchronous Compensator                   |  |  |  |

| SVM           | Space Vector Modulation                          |  |  |  |

| THD           | Total Harmonic Distortion                        |  |  |  |

| THSPWM        | Third Harmonic Sinusoidal Pulse Width Modulation |  |  |  |

| TRIAC         | Triode for Alternating Current)                  |  |  |  |

| VSC           | Voltage-Source Converter                         |  |  |  |

| VSD           | Vectorial Switch Decomposition                   |  |  |  |

| WBG           | Wide-Bandgap                                     |  |  |  |

| ZOH           | Zero-Order Hold                                  |  |  |  |

|               |                                                  |  |  |  |

# RESUMEN

Este trabajo pretende unir el conocimiento actual sobre controladores multitasa o multifrecuencia (*multirate*) con técnicas de diseño para convertidores conectados a la red, en este caso concreto, a la red alterna (AC) de Media Tensión. Por tanto, se estudian las contribuciones multirate realizadas hasta la fecha, así como todo lo relacionado con la modulación de la señal de control para los convertidores. Las implicaciones temporales del actuador DSPWM se relacionarán con el análisis multitasa, así como se explicarán posibles alternativas para aplicaciones con una frecuencia de muestreo menor que la de modulación. Finalizando con la explicación y presentación de resultados de controladores trabajando entre dos frecuencias o tasas, mediante simulaciones del convertidor disponible en laboratorio.

**Palabras clave**: Tiempo discreto, Modelado, Media tensión, Convertidores de potencia, Multitasa.

# Abstract

This work aims to unify the current knowledge about multirate controllers with design techniques for grid-tied converters, in this occasion, connected to Medium Voltage AC grid. Therefore, the multirate contributions, that have been given so far, are studied, as well as everything related to modulation techniques for power converters. The temporal implications of the DSPWM actuator will be correlated to multirate analysis, in addition to possible alternatives for applications with a lower sampling frequency than modulation one. Finalizing with explanations and result demonstrations of controllers working between two frequencies or rates, by means of the available power converter in laboratory.

Keywords: Discrete-time, Modelling, Medium Voltage, Power converters, Multirate.

### EXTENDED ABSTRACT

Multirate control is an unusual technique in power electronics, so this works aims to give an alternative for controller designers in power electronics when hardware or software constraints can be found. These limitations could be related to sampling and actuation rates, when hardware ADC or switching frequency, respectively, cannot be correctly synchronized. Even, computational burden can lead to this situation, if the designer wants to maximize the performance of the converter.

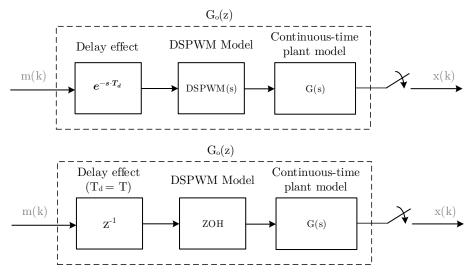

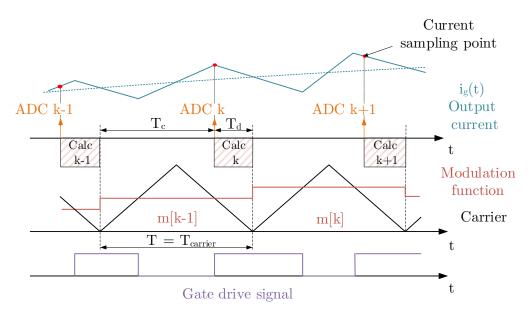

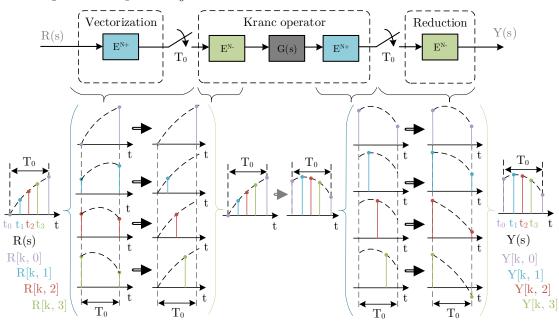

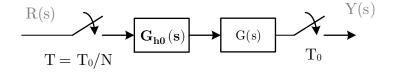

These reasons lead to a detailed analysis of modulation techniques, directly related with control actuation, and current proposals in power electronics. The DSPWM is an interesting modulation technique, that is profoundly analyzed in this document to keep clear what are the consequences of applying multirate methods to it. Besides, its temporal characteristics are related with the modified Z-transform, which is also linked with multirate analysis. In addition, two multirate studies in power electronics are presented, each of them with a different point of view. One takes internal representation to get a single-rate equivalent that is analyzed with usual techniques of stability and robustness. Hence, the internal representation using Kranc methodology with three different situations is introduced. The other example uses the external representation to also get a single-rate equivalent to analyze its stability and robustness.

The complex-coefficient systems are usual in power electronics due to phasor nature of controlled variables. For that reason, this document works with complex-valued models of the L-filter for each reference frame to be studied. Besides, its discretization is detailed, because computational delay interferes in rotating reference frame transformation.

Then, some multirate applications must be presented to give context to the possibilities of multirate control in power electronics. Firstly, a relationship is inferred between DSPWM and SHE modulation techniques with a sinusoidal extrapolation technique. For DSPWM, the crossing between modulating and carrier signals could compromise the switching device, so proper gate drive signals must be generated. For SHE modulation, this document presents a possible alternative using polynomial extrapolation, but the correct extrapolation is the same taken for DSPWM. These situations are related to multirate current control, but there are possibilities for hierarchical control in power converters too. Frequently, every control level has its own rate, so maybe multirate techniques could be used for enhancing the overall system performance. To associate this later concept with an actual application, few explanations are given about Microgrids.

The main goal of this document is to introduce multirate analysis in the current control loop. The multirate approach needs single-rate control structures on which to be based, so two complex-valued controllers in stationary and rotating reference frame are introduced. Then, a possible example using internal representation (space-state) is shown to obtain single-rate equivalents that allow the designer to use habitual stability and robustness analysis tools. Detailed simulation will endorse the single-rate equivalents.

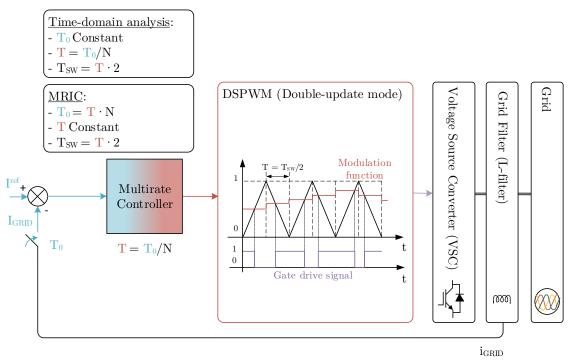

Nevertheless, a more sophisticated multirate technique must be used to properly control the system. Consequently, a model-based dual-rate controller is presented. In these proposals, the sampling frequency is lower than the modulation one, so the goal is to maximize the performance of the control system and to obtain the same response that could be obtained by using a fast single-rate controller. The controller gets extraordinary results that are endorsed by detailed simulation of the grid-tied power converter.

The grid-tied power converter parameters are those from the 3L-DNPC-VSC in research laboratory, which works in Low Voltage. In this way, the simulation results that will be shown here can be compared with future experimental test. The issue is in MV, but tests are adapted to available resources.

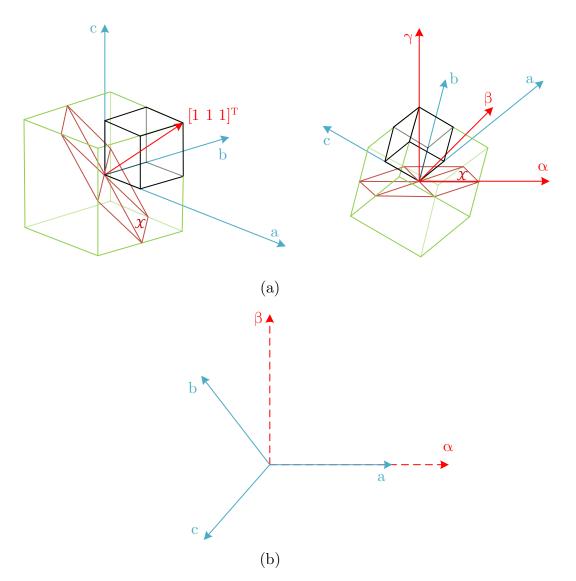

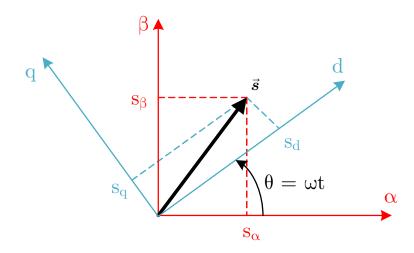

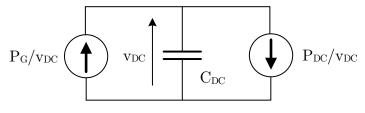

Furthermore, appendix given in this document will help to the reader to consider the bases that supports some concepts. Firstly, modified Z-transform is explained and related with multirate systems. Then, vector representation of three-phase systems is briefly introduced, because it is needed for controller design and plant modelling. Finally, two basic control structures in VSC are presented.

#### CHAPTER 1. INTRODUCTION

#### 1.1. Motivation

Nowadays, the electric energy powers the world and its demand is growing every year, what is a challenge because the electric power system complexity rises with it. The complexity increases with the renewable energy resources added by the increasing demand of  $CO_2$ -free energy, which is enforced by the laws. The European Union target is a 20% final energy consumption from renewable sources by 2020. Each EU country is committed to reach its own national renewable energy action plan, which includes sectorial targets for electricity, heating and cooling, and transport. Figure 1.1 shows the trend in the recent years. Besides, the Europe 2020 target is a 20% increase in energy efficiency. In absolute terms this means that by 2020 EU energy consumption should not exceed 1483 Mtoe (million tonne of oil equivalent) of primary energy or 1086 Mtoe of final energy.

Figure 1.1. Share of renewable energy in gross final energy consumption. Source: Eurostat

Figure 1.2. Primary energy consumption and final energy consumption. Source: Eurostat

The energy losses occurring during energy transformation (particularly electricity generation), transmission and distribution determine the difference between primary and final energy consumption. In Figure 1.2 is shown the path over the past years.

A new target of at least 27% of final energy consumption is set for 2030 for helping the EU meet its energy needs beyond 2020. The European Commission wants to make the EU a global leader in renewable energy. These reasons lead to an active research of renewable energy sources and efficiency in each energy conversion.

The distribution approach is changing in the recent years, since the spreading of distributed generators. The management of small distributed producers, essentially renewable sources, have become an important issue to get a reliable and stable network. There is where the power electronic systems have an important role as they could manage the energy exchange between grid and producers, as well as grid quality. Hence, the new distribution approach is a smart high-power medium-voltage (MV) system, where power converters are used in applications such as motor drives, flexible AC transmission systems (FACTS), renewable energy resources integration, or efficient conversion. Note that IEC 60038 defines each voltage level as it is shown in Table 1.1.

| IEC voltage range  | AC three-phase RMS voltage [V] |  |  |

|--------------------|--------------------------------|--|--|

| Extra-low Voltage  | < 50                           |  |  |

| Low Voltage        | 100 to 1000                    |  |  |

| Medium Voltage     | 1000 to 35000                  |  |  |

| High Voltage       | 35000 to 230000                |  |  |

| Extra-high Voltage | > 245000                       |  |  |

Table 1.1. Voltage ranges. Source: IEC 60038

On one hand, Flexible AC Transmission Systems (FACTS) technology enhances the controllability and increase power transfer capability of the power system. FACTS technology lead to new opportunities for controlling the power and improving the usable capability of lines. The used technology is power electronic-based and other static controllers, where the words "other static controllers" is referred to those which are not based on power electronics. The power electronic-based static controllers provide control of one or more AC transmission system parameters as line impedance, angle, or voltage.

On the other hand, power electronic converters provide an efficient and stable power flow between the utility grid and renewable sources, and even among forms of transport. Electric vehicles need converters to charge their batteries and most trains are electric-based. Also, metropolitan trains need an efficiency energy consumption, so the regenerative brake provides an energy recovery to the own railway electric grid through power electronic converters.

The power electronic converters are essential to enhance grid flexibility and to achieve the new efficiency requirements. Therefore, the power converter operation must be reliable, flexible, efficient, and economic, so must the controllers. The power switching device is the essential component of each converter. The semiconductor switching device evolution has been always aimed to achieve an ideal switch. And evaluated switching device characteristics are the operating frequency, the blocking voltage, and the device current. Therefore, an ideal switch would have infinite operation frequency, infinite blocking voltage, null drop voltage when on, and null drive current when off and infinite when on. That is no conduction or switching losses.

The commercial devices are not ideal, and they never will, so each kind of semiconductor switching device is appropriated to each application according to the system requirements. Besides, the switching frequency determines the control rate for MV converters as it is intrinsically related by the actuator. Although multilevel converters could improve the management of more voltage, current or higher equivalent switching frequency, some MV converters use more economic topologies where the device switching frequency still constrains the control rate.

#### 1.1.1. Flexible AC Transmission System (FACTS) controllers

FACTS controllers improve the power transfer capability of existing transmission and distribution lines. The delivery period of FACTS technology is lower than the installation of new lines, which makes this technology more attractive.

FACTS controllers could be classified into four categories[1]:

- a) Series controllers: Could be a variable impedance, or a power electronic based variable source of main frequency, subsynchronous and harmonic frequencies (or a combination) to serve the desired need. Essentially, it injects voltage in series with the line.

- b) Shunt controllers: May be variable impedance, variable source, or a combination of these. Essentially, it injects current into the system at the point of connection. If the injected current is in phase quadrature with the line voltage, this controller only supplies or consumes variable reactive power. Otherwise, a phase relationship involves a real power consumption.

- c) **Combined series-series controllers**: Could be a combination of coordinated series controller in a multiline transmission, or a unified controller which provides independent series reactive compensation and transfers real power.

- d) **Combined series-shunt controllers**: Could be a combination of coordinated series and shunt controller, or a unified controller which provides independent series reactive compensation and transfer real power. They inject current into the system with the shunt part and voltage in series in the line with the series part.

The different types of FACTS Controllers are summarized in Figure 1.3. The application defines the type of controller, e.g. if the purpose is to control the current/power flow and damp oscillations, the series Controller for a given rated power is more powerful than the shunt Controller. The shunt Controller is more willing to control voltage at and around the point of connection through the injection of reactive current, alone or a combination of active and reactive current for a more effective

voltage control and damping of voltage oscillations. The combination of the series and shunt Controllers can provide the best of both, that is an effective power flow and line voltage control. Also, a Controller with storage (large DC capacitors, storage batteries, or superconducting magnets) is much more effective for controlling the system dynamics, i.e. the dynamic pumping of active power. In addition, a converter can be designed to generate the compensate waveform to act as an active filter. Each one has its benefits and attributes, and a preliminary evaluation is needed.

DC Link

Storage

(h) Series Controller with storage (i) Shunt Controller with storage (j) Unified series-shunt Controller with storage

Storage

Figure 1.3. Basic types of FACTS Controllers

Storage

To sum up, every FACTS is a variable impedance that is focused on the needed application.

Besides, for the converter-based controllers there are two types: voltage-sourced converters (VSC) and the current-sourced converters (CSC). CSC topology is used in high-power drivers, where GTO and IGCTs are the switching devices. The CSC operates at fixed current while the voltage is modulated. The most common topology is the VSC due to its controllability.

In summary, FACTS controllers will ensure the power system stability, and they will be enhanced by wider area control information systems.

#### 1.1.2. Industrial applications

New highly efficient power electronic technologies and suitable control strategies are needed to reduce energy waste and to improve power quality [2]. Energy efficiency is a potential field in electric motor driven systems. Therefore, the aim is to introduce efficient MV adjustable speed drives in industrial applications.

In MV drives is fundamental a high-quality voltage and current at both terminals, input, and output. The waveforms are related to: topology used, the application, the control algorithm, the size of the filter, and chosen switching frequency. There are different approaches for the optimal solution, and each factor has a different weight in it. The hardware characteristics are not in the scope of this document, but some relation between factors must be considering. An elevated switching frequency increases the switching losses, what reduces the maximum output power, but a switching frequency reduction increases the harmonic distortion in the line and motor side current waveforms and it lead to solution with expensive LC filters. The goal is a converter that reduces harmonic distortion with low switching frequency, and this is accomplished with multilevel converters.

Multilevel converters improve the voltage waveforms compared to the basic two-level voltage source converter (2L-VSC), as they enhance power quality, reduce switching losses, and obtain a high voltage capability. The 2L-VSC cannot be used in applications where is required high converter efficiency and low harmonic distortion, because the LC filter constrains the low carrier frequencies.

The 3L neutral-point-clamped voltage source converter (3L-NPC VSC) is the most efficient among available solutions, and it is the preferred choice in several industrial MV applications [3]. For example, Table 1.2 gives some voltage and power rating of usual industrial MV drives. It requires high switch power, but the expense in the LC filter is moderate. Also, the high switching losses share causes a reduction in installed switch power at low switching frequency. The additional attractive features are: simple grid transformer, a small DC link capacitor, and modular realization of common DC-bus configurations. This multilevel topology is usually compared to flying capacitor voltage source converter (3L / 4L-FLC VSC), and series-connected H-bridge voltage source converters (5L-SCHB VSC). The FLC VSC rises the expense in capacitors, and the SCHB requires a complicated grid transformer, and high DC-link capacitance.

| Manufacturer | Type                 | Power<br>(MVA) | Voltage (kV)           | Semiconductor |

|--------------|----------------------|----------------|------------------------|---------------|

| ABB -        | ACS 1000             | 0.3 - 5        | 2.3; 3.3; 4.0; 4.16    | IGCT          |

|              | ACS 6000             | 3 - 27         | 2.3; 3; 3.3            | IGCT          |

| Siemens      | Sinamics<br>SM120 CM | 6 - 13.7       | 3.3 - 7.2              | MV IGBT       |

|              | Sinamics<br>SM150    | 5 - 28         | 3.3                    | IGCT          |

|              | Sinamics<br>GM150    | 0.6 - 10.1     | 2.3; 3.3; 4.16; 6; 6.6 | MV IGBT       |

| Alstom       | VDM7000              | 0.3 - 8        | 3.3                    | PP-MV-GTO     |

| TMEIC GE     | Dura-Bilt5i<br>MV    | 7.5            | 4 - 4.2                | IGBT          |

Table 1.2. Market overview of industrial 3L-NPC-VSC MV Drives. Source: [2]

Therefore, the 3L NPC VSC is characterized by a relatively small DC-link capacitor, a simple power circuit topology, low number of components, and straightforward protection and modulation schemes. These features make it a competitive solution for a large variety of low and medium switching frequency applications.

The 3L-NPC VSC has positioned as an essential in more conventional high-power AC motor drive applications like conveyors, pumps, fans, and mills. Also, a back-to-back configuration is possible with this topology, which is attractive for regenerative applications, as in regenerative conveyors for the mining industry or grid interfacing of renewable energy sources. The regenerative applications are also present in transports, as electric trains, or vehicle applications.

As it is mentioned before, the control algorithm is one of the factors related to the waveform quality and converter response, and it is the taken power converter approach in this document.

Figure 1.4. SINAMICS SM120 CM Medium Voltage drive. Source: Siemens web

#### 1.1.3. Power semiconductor devices

Every power converter is composed of semiconductor devices and the characteristics of each one determines its applications. The desirable characteristics on any of them are:

- 1. On-state characteristics: High-current rating, and low forward voltage drop.

- 2. **Off-state characteristics**: High forward and reverse voltage blocking capability, and low leakage current.

- 3. Switching characteristics: Low power and controllable turn-on and turn-off, high dv/dt and di/dt transitions ratings, and low switching power losses.

- 4. **Gate characteristics**: Low gate-drive voltage and low gate-drive current, and low gate drive power.

- 5. Fault withstanding capability: Withstand fault current for a long time.

- 6. **Thermal stability**: Low thermal impedance coefficient from the internal junction to ambient.

Hence, among other characteristics, the ideal device features high handling current, high blocking voltage and high switching frequency. However, there is no ideal device, and an equilibrium between these characteristics is obtained in each power semiconductor device.

Before start with an overview in the technologies and trends in power semiconductor devices, a first classification might be shown to differentiate them as a function of its controllability [4]:

- a) Uncontrolled turn-on and turn-off: Commonly known diodes.

- b) **Controlled turn-on and uncontrolled turn off:** A category that includes SCR (Silicon Controlled Rectifier), and TRIAC (Triode for alternating current).

- c) Controlled turn-on and controlled turn-off: This category can be divided into two distinct groups:

- 1. **Current-controlled devices**: A positive or negative current pulse is needed to open or block them, respectively. In this category can be found: BJT (Bipolar Junction Transistors), GTO (Gate Turn-Off Thyristors) and IGCT (Integrated Gate-Conmutated Thyristor).

- 2. Voltage-controlled devices: Also known as MOS (Metal-Oxide-Semiconductor) gate or isolated gate. Since their low control power or high switching frequency, the power semiconductor research and the technological efforts involved in manufacturing have been focused on evolving these devices.

- i. MOSFET power transistors (MOS Field Effect Transistors): They have high switching frequencies (tens or hundreds of kHz) with low power losses. Their limitation is an increase in the on-state resistance along with the rise of the maximum blocking voltage rating, which lead to important power losses during conduction. Therefore, they are not used in high power applications.

ii. Insulated Gate Bipolar Transistor (IGBT): It is a mixture with the low on-state power losses of BJT, and the high switching frequency (low power losses) of MOSFET. It is a transistor that can be used with high-medium switching frequencies (units or tens of kHz) and megawatts power. It is the most widely used in power electronics.

As it was mentioned before, the characteristics of each semiconductor device determine what is the suitable application, as is shown in Figure 1.5.

Figure 1.5. Classification of power devices according to their rated power and switching frequency, and their applications. Source: Yole Développement web

Silicon technology is the preferred choice in semiconductors, but in recent years there is an increasing penetration of wide-bandgap (WBG) semiconductors technology [5]. Silicon carbide (SiC) and gallium nitrite (GaN) devices are reaching different levels of maturity, with several manufacturers offering packaging solutions. In Figure 1.6 is shown the perspective on WBG technologies.

Figure 1.6. Perspective on WBG technologies in terms of frequency and power. Source: [6]

Silicon IGBT is used in high power applications, but the switching frequency is constrained to 2-5kHz due to high switching losses, so the Total Harmonic Distortion (THD) increases. The SiC based MOSFETs and IGBTs for high voltage devices are developed to mitigate these issues. The reduction in the specific on-state resistance in SiC-based devices compared to Si devices results in lower conduction loss.

The SiC MOSFETs feature very low on-state resistance and excellent switching performance, translating into more efficient and compact systems. These devices combine the excellent switching performance of Si MOSFETs and low on-state resistance of Si IGBT.

Hence, the rising in the switching frequency capabilities in high voltage applications around a boundary of 10kHz can change control concepts. Many applications have high computational burden, what constrains the switching frequency if a digital control is designe following conventional structures of modulation. New perspective frame is obtained with different sampling/control rate and modulation/switching rate.

## 1.1.4. Multirate approach

The multirate system is a structure where two or more variables are updated with different rates or frequencies. Usually, the sampling is considered synchronous and periodic, which is known as conventional sampling, but the samplers might be not synchronized, or they can be variable in time.

Some practical applications have economic and technological constraints that implies the use of control schemes where sensor sampling and control calculation of the actuation is updated with different rates or frequencies. One possible situation could be found when a MV power converter has a low frequency switching device, but the sampling and control frequency could be faster to get a better response. It is known as down-sampling (decimation), and its detailed modelling could improve the system performance, and get the better resources exploitation of the system. However, the inverse situation can be found when the actuation is faster than sampling and control. It is known as up-sampling. The later concept will be explained in this work with few examples as a different digital implementation of SPWM or SHE modulation techniques, or applications where the computational burden of additional control algorithms (e.g. impedance calculation) requires a stability analysis of the control loop. In addition, all hierarchical control with different rates (higher control level, lower bandwidth) can maximize its response with a correct multirate analysis of the system.

Besides, in multivariable systems might be advantageous to get different sampling frequencies for each different loop, so the system performance is improved, and the computational burden is reduced. This is related to what was previously mentioned as additional control algorithms.

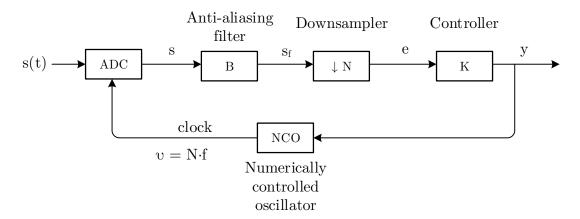

In power electronics field, the multirate analysis has a wide niche, because there are few applications in literature correctly modelling or using the multirate approach. Most power electronics applications have their scope in grid synchronization part, but each one of them search for a signal processing to improve the signal acquisition with a digital antialiasing filter, consequently a fast synchronization is obtained [7][8]. Also, a harmonic estimation can be reached with a multirate digital signal processing [9]. On the other hand, there are some multirate applications in DC/DC that are not in the scope of this work, but they are willing to use some techniques shown here. Thus, this document will only analyze a DC/AC converter in the following chapters.

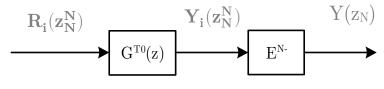

Figure 1.7. Simplified block diagram of single-rate and multirate example of currentcontrolled systems

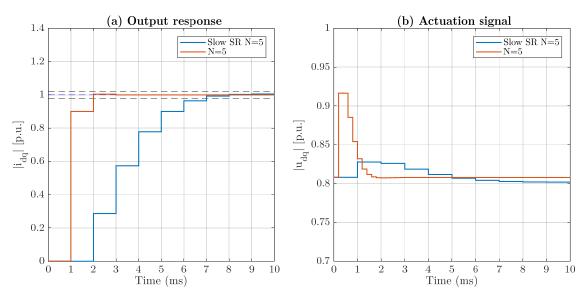

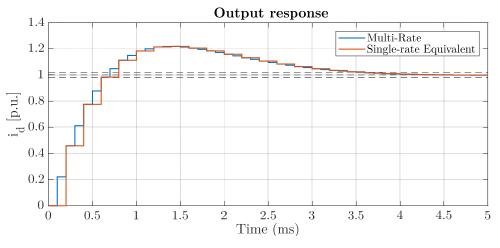

Figure 1.8. Comparison of slow and fast single-rate responses with the multirate approach of a current-controlled system.

For example, Figure 1.7 depicts a possible application where the power converter switching frequency is faster than sampling one. How can the designer obtain an optimum response from the current controller? If the controller works at the slowest rate, that is the sampling rate, the switching frequency will not be optimally used. Hence, the answer is a multirate controller with an input at slow rate and an output at fast rate.

Figure 1.8 shows the response of VSC to step change for a current control loop with a slow single-rate controller (constrained by sampling) and its multi-rate equivalent. The multi-rate controller is based on the possible fast single-rate equivalent, which is designed to reach the steady state in the same discrete steps, so this fast single-rate controller will be faster. Note that N is the multiplier that relates sampling and actuation rates. Detailed information will be given in this work.

# 1.2. Power converter topology

## 1.2.1. Classification

This document is based on the controlling of AC/DC topologies, where a few different types can be found, so the topology used in this document should be located into the MV power converter topologies. In MV, the topologies can be split in two categories depending on the imposed variable (source) regardless to the other one:

- Current-Source Converter (CSC): They operate at fixed current (inductor at DC side) while the voltage is modulated. They are suitable to high-power drives, and the dynamic response is relatively slow [10]. This group can be divided into Pulse Width Modulation (PWM) CSC and Load-Commutated Converters (LCC). The difference resides on the switching device, the former uses GTO or IGCT, whereas the latter uses SCR. These topologies are not in the scope of this document.

- Voltage-Source Converter (VSC): These converters operate at fixed voltage (capacitor at DC side). They are the typical topology due to its controllability. The voltage levels obtained at the AC side define the type of VSC, and all are known as multilevel converters. This term includes all the topologies that can supply an output voltage signal with more than two voltage levels, so a classification is shown based on the type of DC supply [11].

The scope of this document is in the 3-Level Neutral Point Clamped (NPC) VSC. It has the highest converter efficiency among the available solutions and is widely used in many industrial MV applications [3]. The most common 3L NPC VSC use a diode to connect each phase to the neutral point and is known as Diode NPC (DNPC). However, the Active Neutral Point Clamped (ANPC) solution is taking interest in MV applications due to the additional controllability of losses, because the diodes are substituted by voltage-controlled switching devices (e.g. IGBT).

#### 1.2.2. Diode Neutral Point Clamped VSC

The 3L-DNPC-VSC was firstly described in [12] and published in [13], and Figure 1.9 shows electronic configuration of this converter with IGBTs and their corresponding free-wheeling diodes. The DC voltage is split into two capacitors, and a neutral point between them is formed. Therefore, each phase generates three voltage levels:  $+V_{DC}/2$ , 0,  $-V_{DC}/2$ . Usually an unbalance is generated on the voltage at this point, but the control and analysis are not on the scope of this document, so equal capacitor voltage is considered.

| Switching |                | Phase          |       |            |                |

|-----------|----------------|----------------|-------|------------|----------------|

| state     | $\mathbf{S}_1$ | $\mathrm{S}_2$ | $S_3$ | ${ m S}_4$ | voltage        |

| Р         | 1              | 1              | 0     | 0          | $+V_{DC}/2$    |

| 0         | 0              | 1              | 1     | 0          | 0              |

| Ν         | 0              | 0              | 1     | 1          | $-V_{ m DC}/2$ |

Table 1.3. Switching states on the 3L DNPC VSC

The clamping diodes are conducting when the switching devices  $S_2$  or  $S_3$  are activated, so the phase line is connected to the neutral point. The DNPC operating point is represented by the switching states on Table 1.3.

Figure 1.9. Phase structure of a 3L DNPC VSC

The phase current direction determines what device (diode) conducts in the zero (0) switching state. Two equivalent zero states are possible, at the positive or negative half cycle of the phase voltage signal. The devices  $D_{02}$  and  $S_3$  conduct with incoming current, whereas  $D_{01}$  and  $S_2$  conduct with outgoing current. This is depicted in Figure 1.10.

During the voltage positive half cycle,  $S_2$  is always active and output voltage is controlled with the half-bridge formed by  $S_1$  and  $S_3$ , which are complementarily activated. On the other hand, during the voltage negative half cycle,  $S_3$  is always active and output voltage is controlled with the half-bridge formed by  $S_1$  and  $S_3$ , which are complementarily activated.

Figure 1.10. Phase current path in 3L-DNP-VSC: (a)Positive (outgoing); (b)Negative (incoming)

A modulation strategy must be followed to convert the reference signal to activation signals. The following chapter will analyze this issue in detail. The main disadvantage of this three-level topology are the non-homogeneous losses in each branch. This is one of the reasons why the maximum switching frequency is limited to the device with more losses, whereas the others are underutilized.

The number of devices could be variable depending on their characteristics. With MV or HV applications, the switching devices must be connected in series to secure the voltage blocking capability of each device.

# **1.3.** Practical objectives

The scope of this work is to obtain the state of the art of the multirate analysis and implement some of its conclusion to the power electronics field, specifically in MV power converters. It is a hard issue due to the lack of literature in this specific branch of power electronics control applications. To achieve the general aim, the following objectives will be met:

- 1. Researching of current knowledge about multirate control. Multirate bases will be defined.

- 2. Review of power converter modulation strategies. Special emphasis will be shown in the sinusoidal pulse-width modulation (SPWM) and selectiveharmonic elimination (SHE).